I found an interesting remark in the 555 timer contest description:

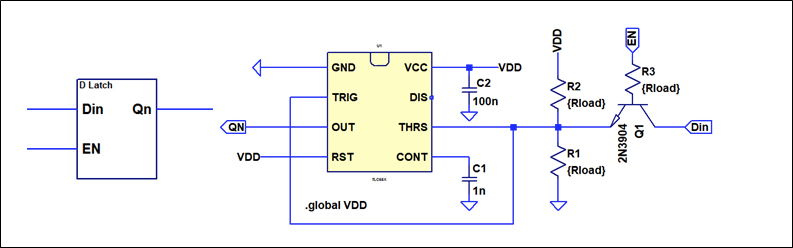

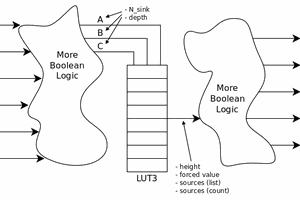

"Should have used a 555." It's mostly applied where a microcontroller and some code are used where a simple 555 circuit would have sufficed.... Maybe you turn the comment right back around and design a microcontroller based on 555s."

This sounds like a challenge! Let's see how far I get. Definitly should not use an NE555 (or 500 of them) for this.

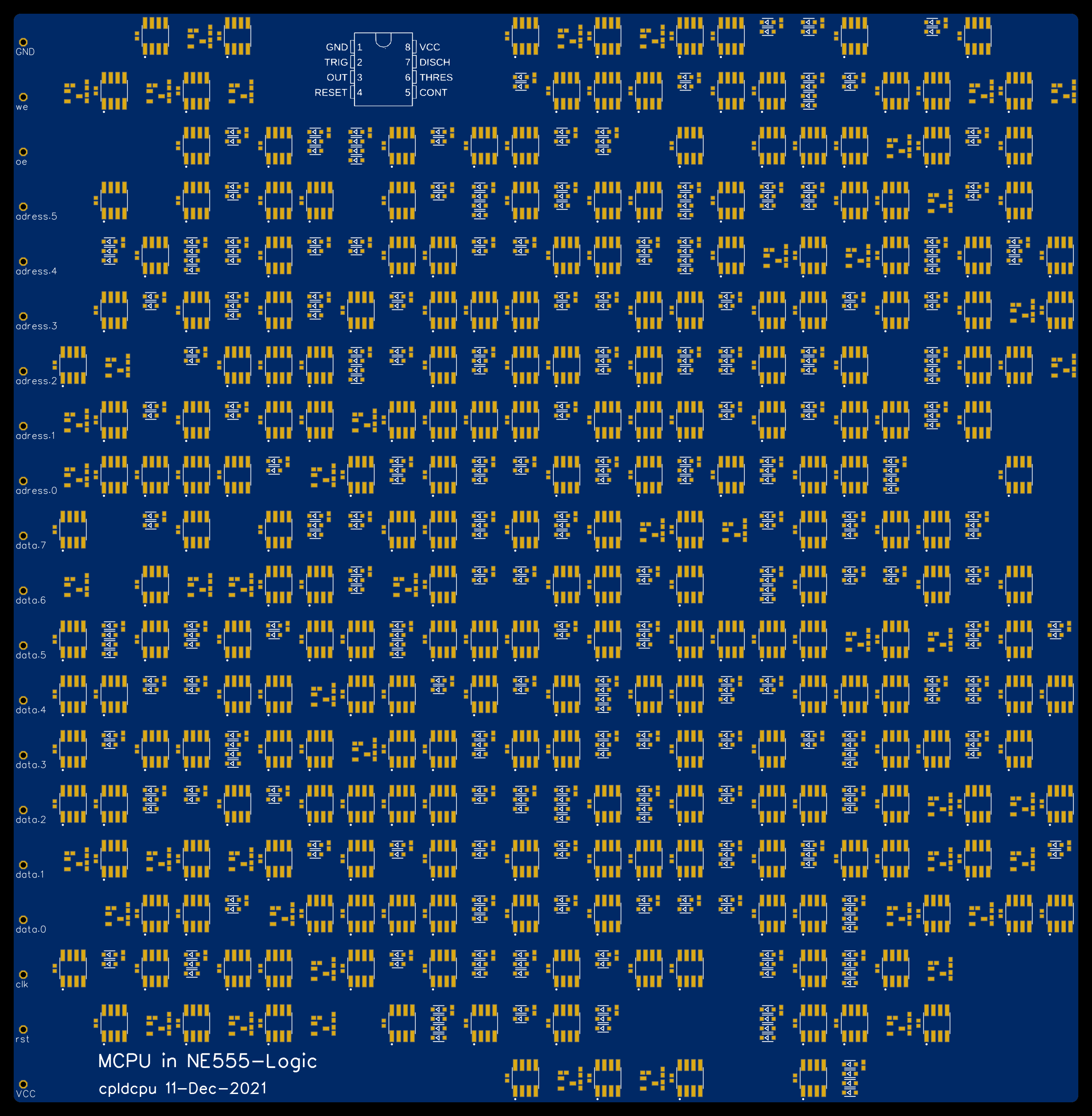

Update: Success!

Click here to view project logs in order

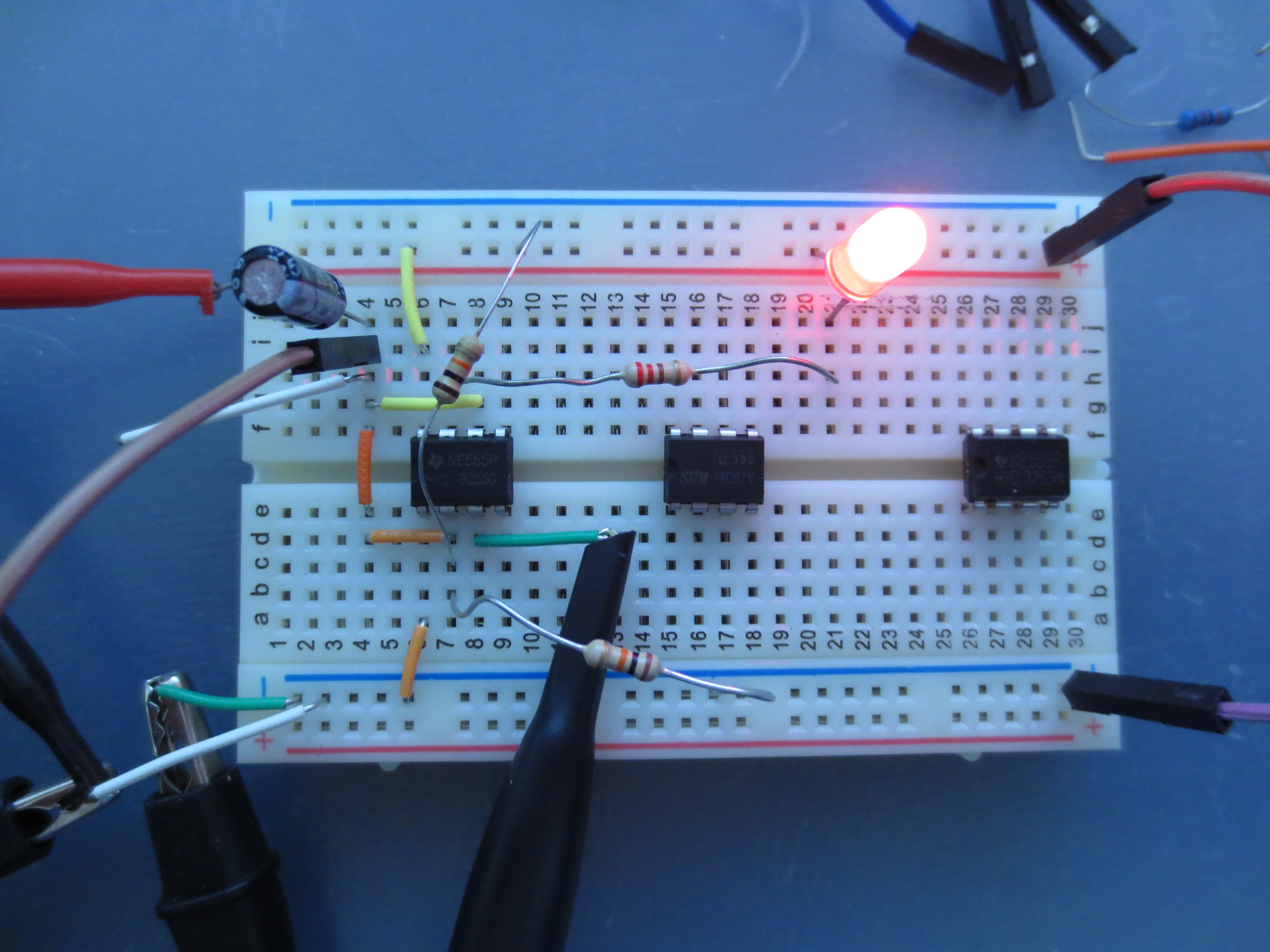

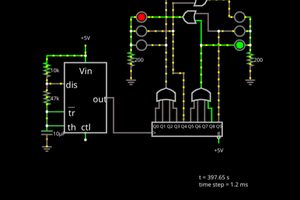

NE555 logic is now proven to be functional in hardware. Check out the companion project.

Tim

Tim

Al Williams

Al Williams

Yann Guidon / YGDES

Yann Guidon / YGDES

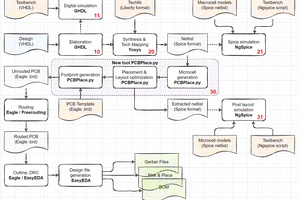

Hi @Tim ! would you share your .Liberty file for this amazing technology ? I don't find it in the .zip file :-/