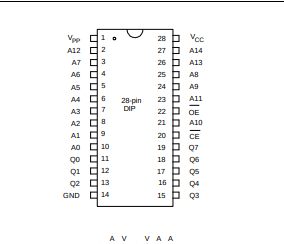

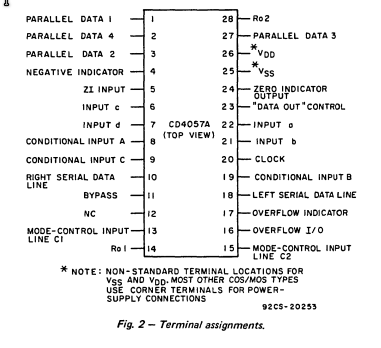

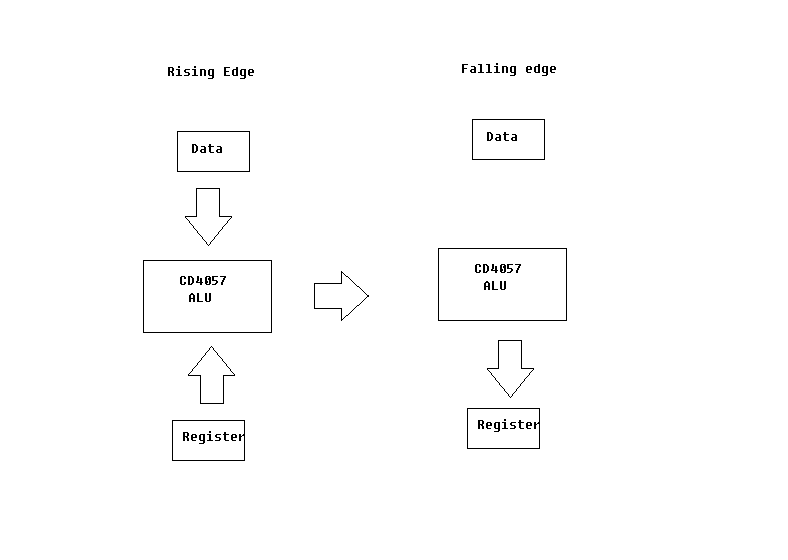

The CD4057A is a 4 bit ALU Like cos/mos part (early cmos) for use in a LSI computers or control systems of its time and was produced by RCA. It boasted many features for parallelism, allowing for intelligently stacking multiple units together to create a wide range of bit depths. It varies somewhat from the 74181, in that it actually has an internal 4 bit shift register with which single bit shifts (across multiple devices). The shift register can be loaded via a function passed to the chip, and also acts as an internal results register on the falling edge of the clock cycle, making this chip kind of close to a 4-bit cousin of the Motorola MC145000 Industrial control unit.

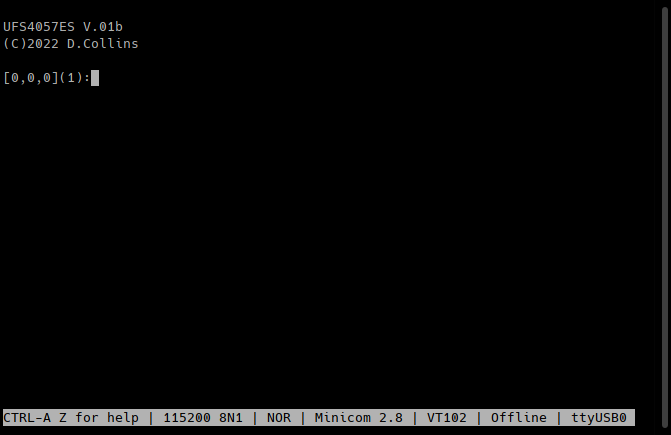

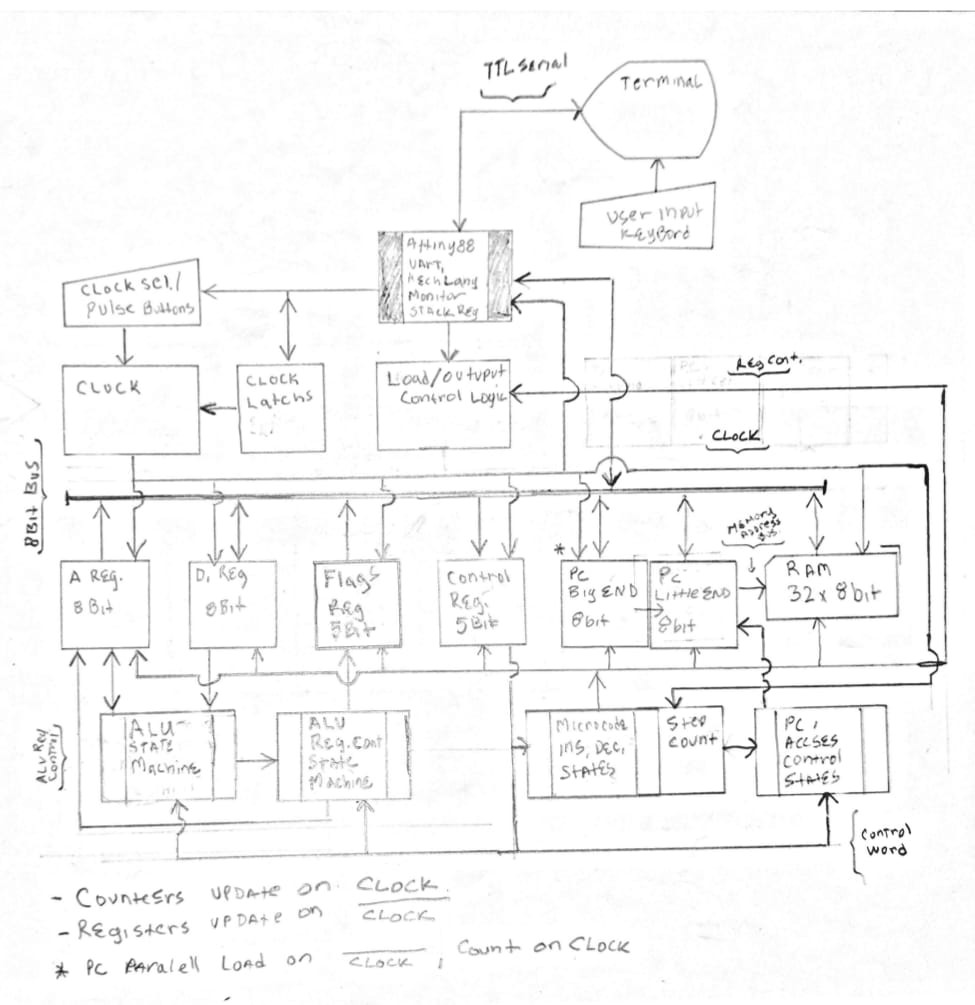

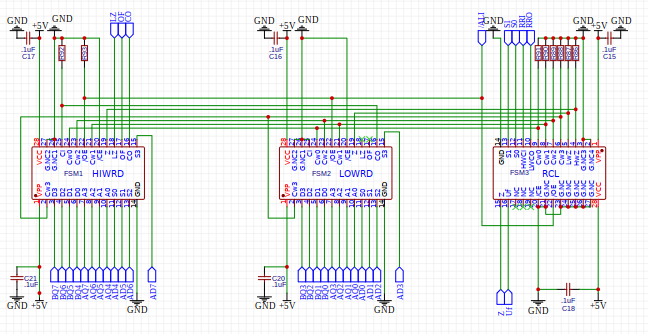

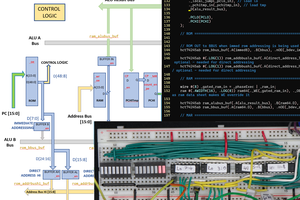

In this project, I am attempting to build up a finite state machine in an EEPROM that pay's homage to this chip and tries to mimic it's functions.

using an EEPROM as a basis for the build, it is unlikely to clone the chip entirely. However, using a 4bit latch it may be possible to build many of the chips functions as A FSM (Finite State Machine).

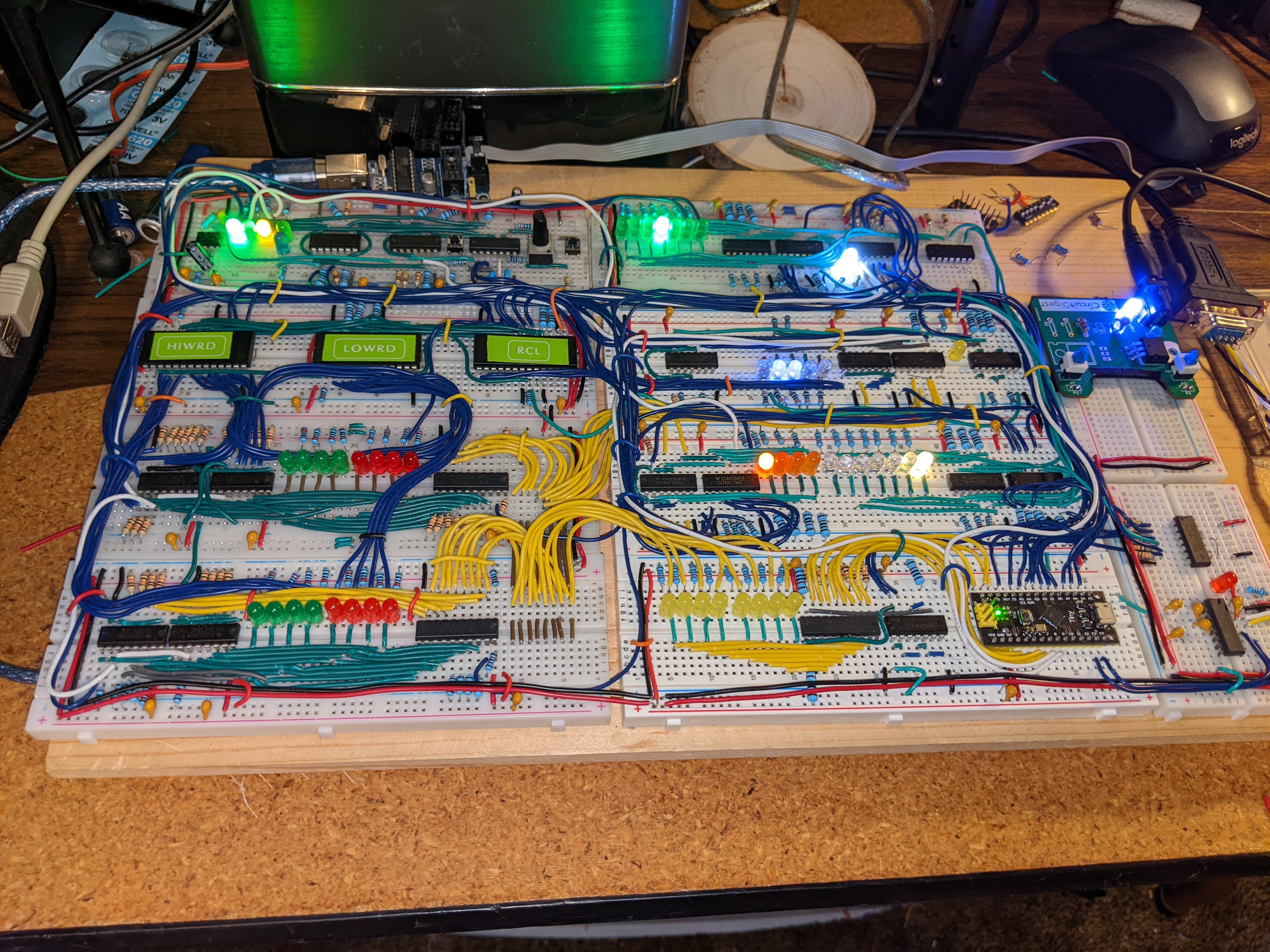

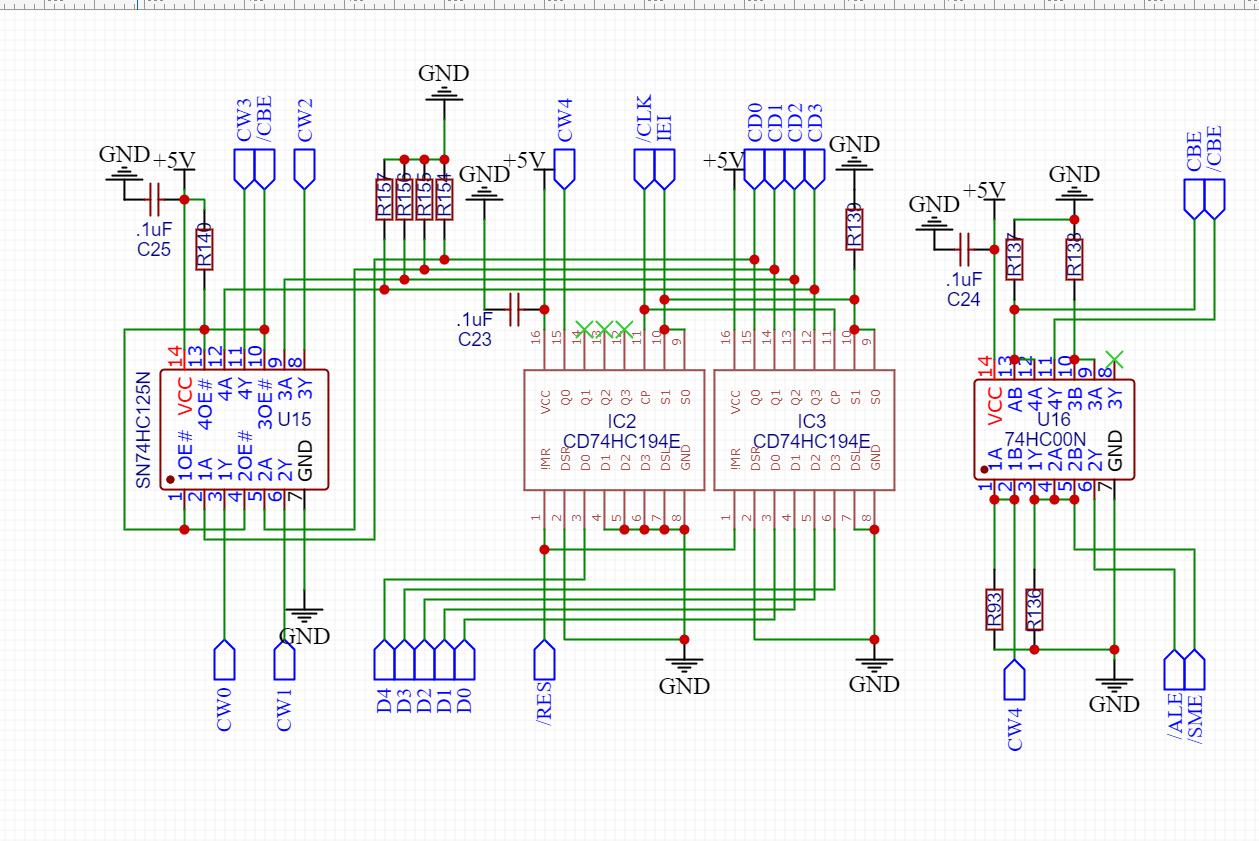

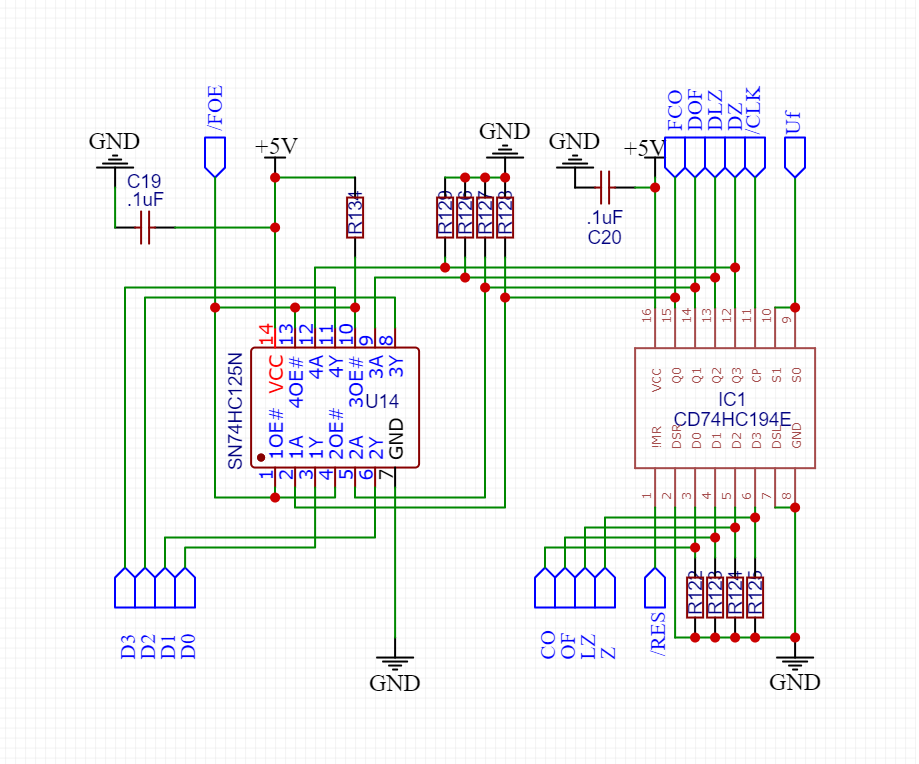

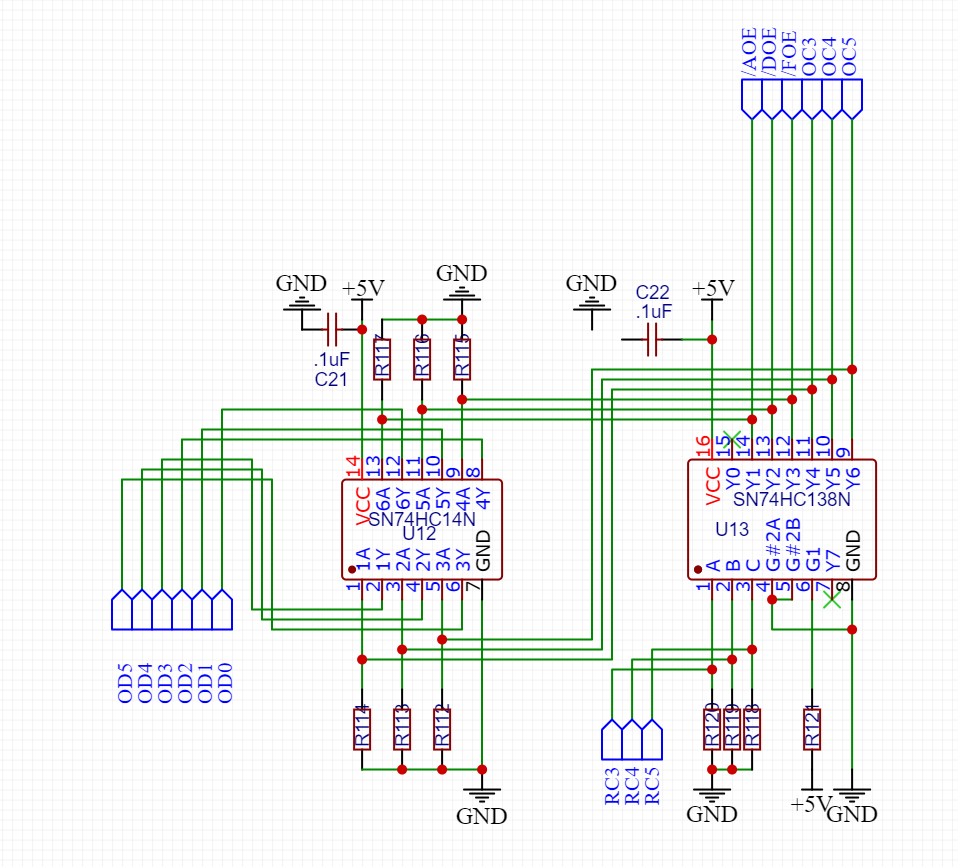

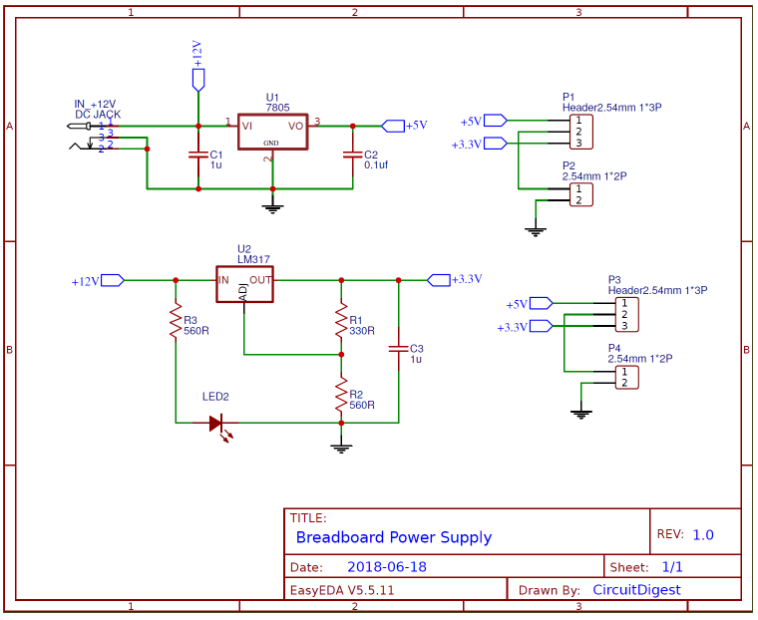

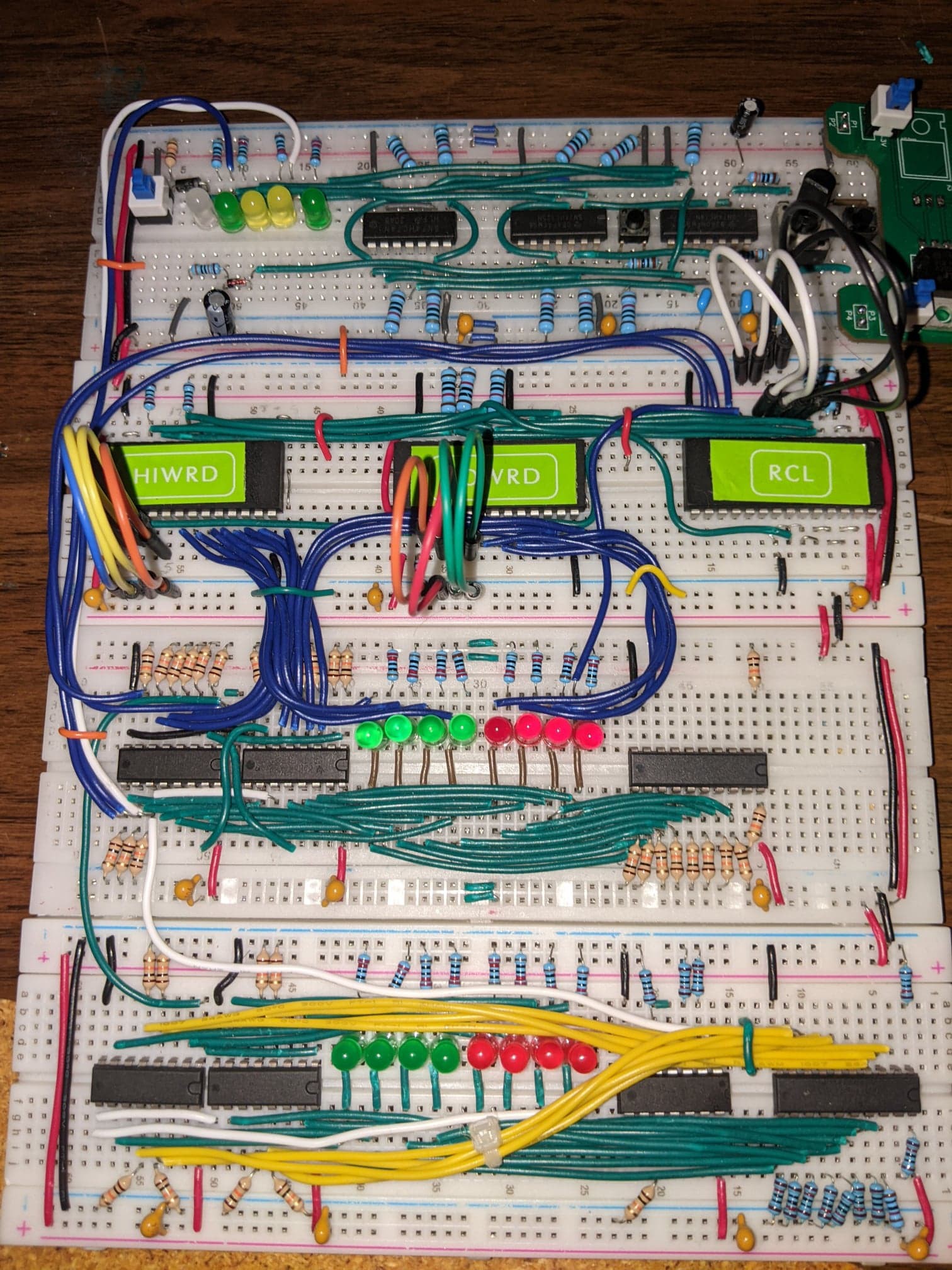

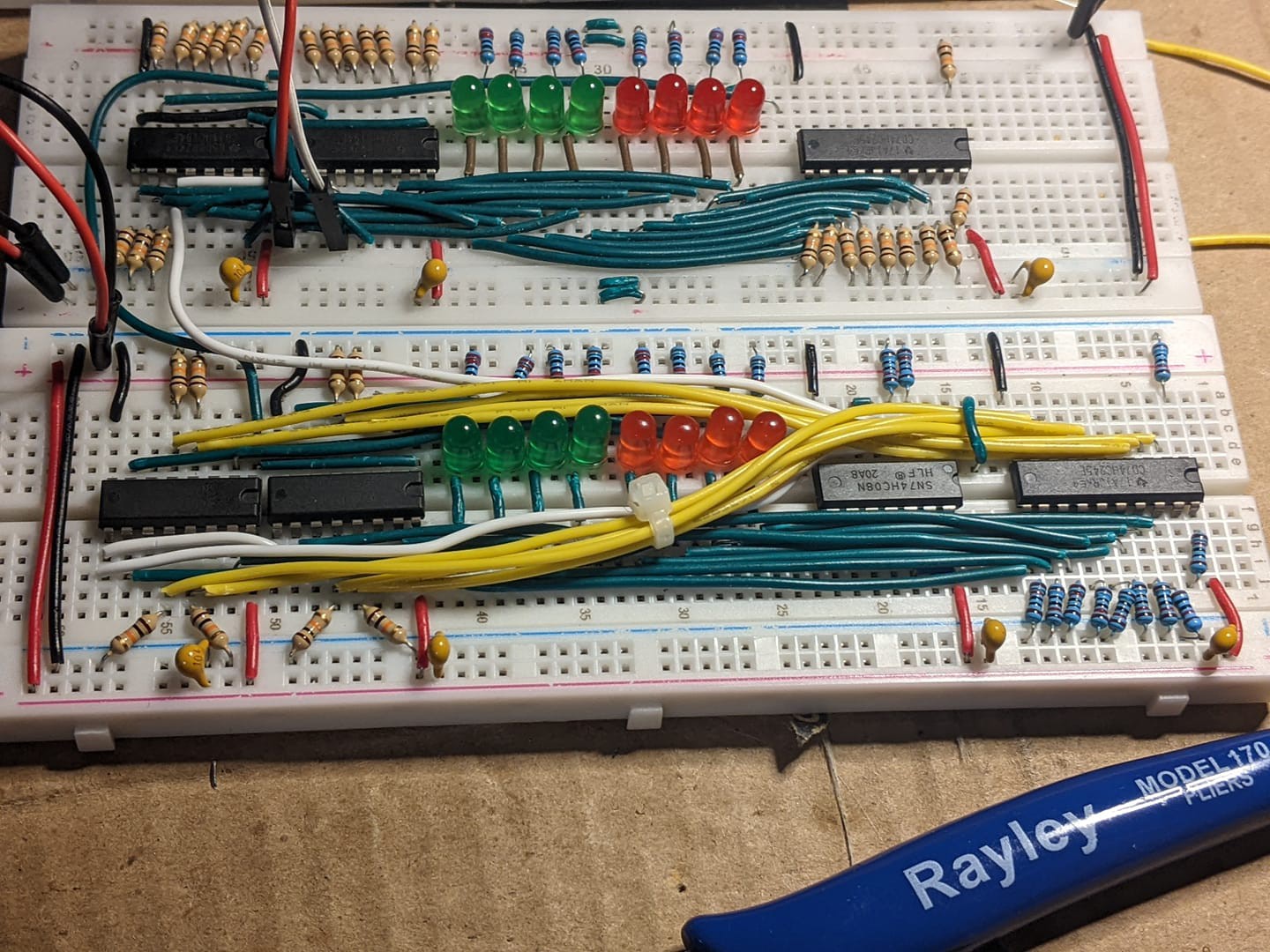

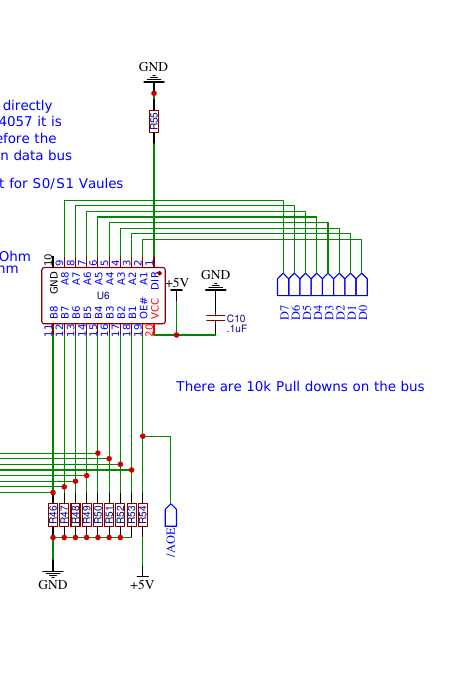

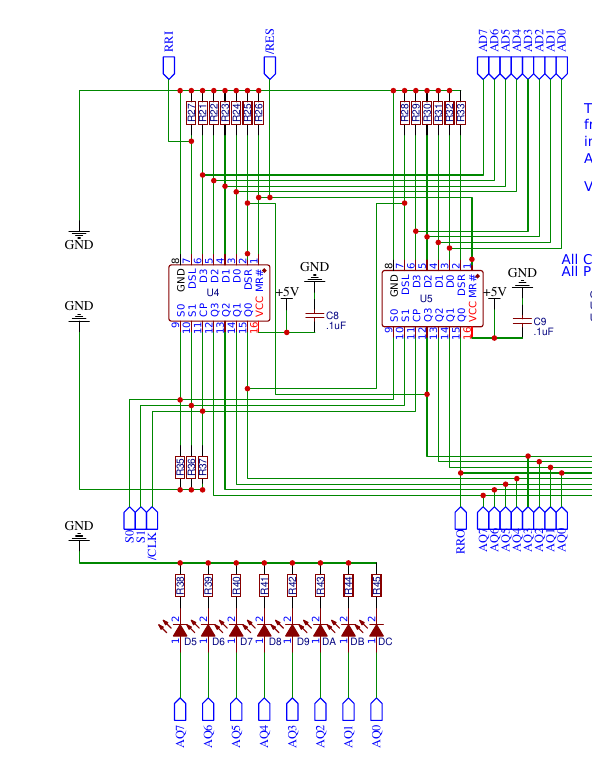

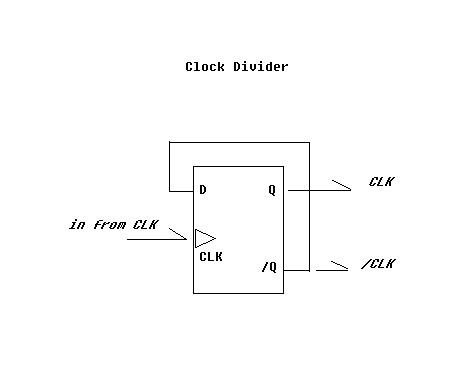

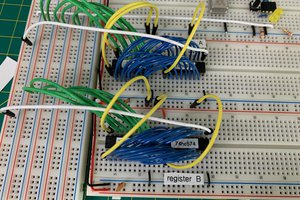

The proof of concept will be a reduced instruction set chip with only 12 input pins. The test set up will consist of 2 eeproms (a low word and a high word), two 4 bit d-latches (updating on the falling edge) a pair of 74hc194 parallel shift registers , a ram chip (or another eeprom) to feed code into the ALU a very simple clock circuit and some led's to display the output.

Dave Collins

Dave Collins

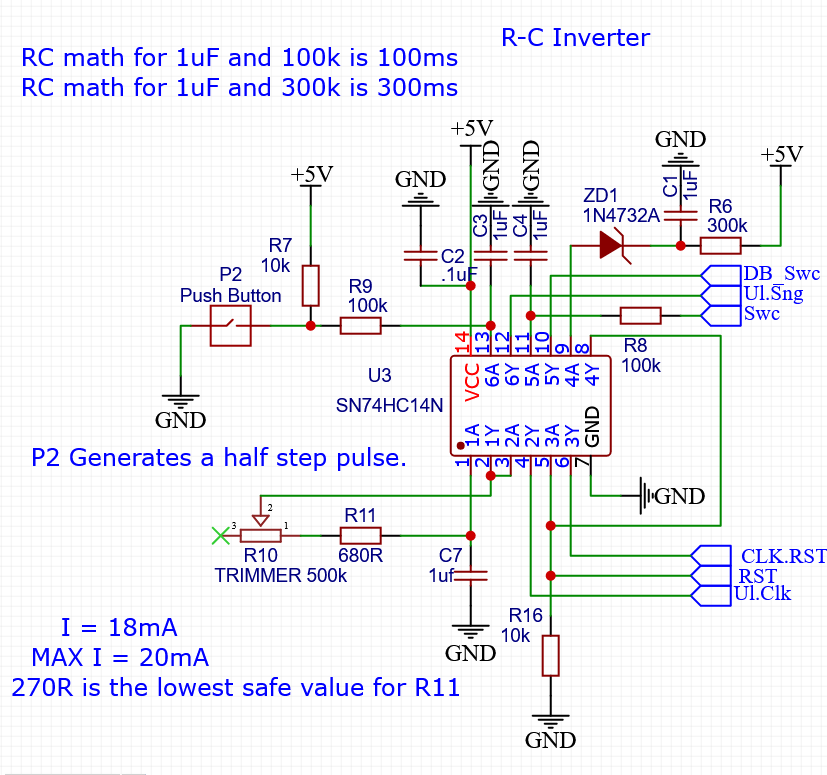

The resistor R11, and Trimmer R10 (combined with C7) provide the R-C network that makes up the main oscillator, as you can see this is essentially two Schmidt Trigger inverters tied together, the first with the resistors connected in feedback to create a very simple square wave oscillator. As I've discussed in previous Logs, this is a very common configuration for building an internal oscillator in a MCU, and has the benefit of being very "Parts Light". The reaming nets on the chip are used for generating Power On Reset (C1, R6 and ZD1), half step pulse (technically a single pulse generated by R9 and C3), and a de-bounced switch for the function select latch (C4 and R8).

The resistor R11, and Trimmer R10 (combined with C7) provide the R-C network that makes up the main oscillator, as you can see this is essentially two Schmidt Trigger inverters tied together, the first with the resistors connected in feedback to create a very simple square wave oscillator. As I've discussed in previous Logs, this is a very common configuration for building an internal oscillator in a MCU, and has the benefit of being very "Parts Light". The reaming nets on the chip are used for generating Power On Reset (C1, R6 and ZD1), half step pulse (technically a single pulse generated by R9 and C3), and a de-bounced switch for the function select latch (C4 and R8).

Jorj Bauer

Jorj Bauer

John Lonergan

John Lonergan

Charlie Smith

Charlie Smith

Brandon Reinhart

Brandon Reinhart

Love to see old devices brought back to life! I wonder if the equivalent function would fit into a GAL22V10...