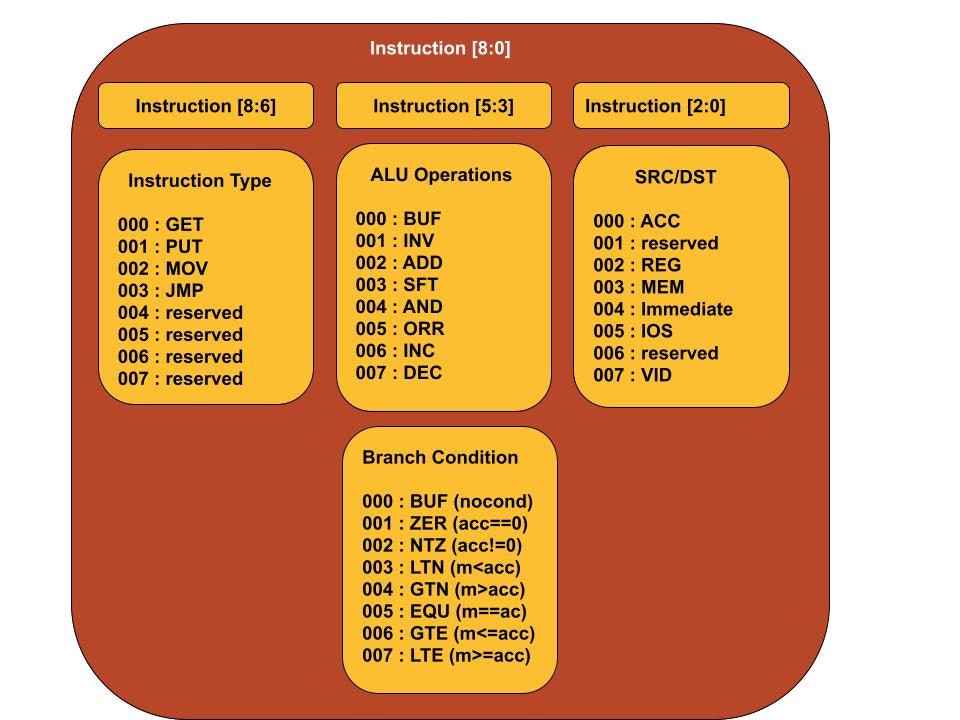

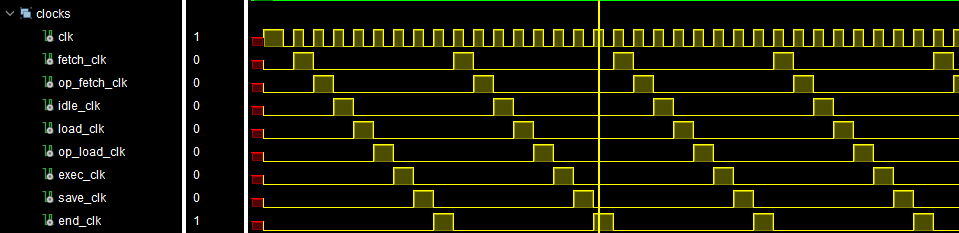

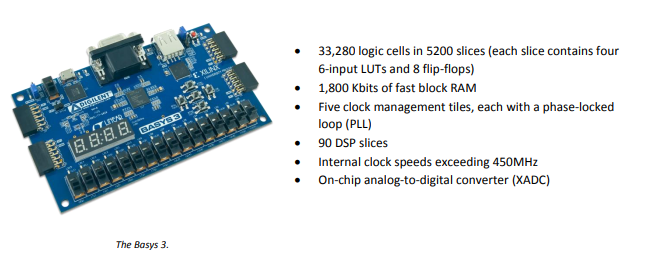

This project is implemented on a (somewhat dated) Xilinx Artix-7 FPGA board, the BASYS 3 development board. The specs for this CPU of mine are decidedly retro - 100MHz clock ( 12.5MHZ instruction execution frequency), 9 bit address and data bus. So only 512 bytes of memory. But not bytes, since they're nine bits.

People will say you can have a 9-bit byte, and that 'byte' is a generic term for the smallest addressable quantity in a system. Technically true, but still confusing. Standards for IP packets avoid using 'bytes' for this reason and when they want to refer to an 8-bit quantity, they call it an 'octet'. So for this system, the equivalent name I discovered was 'nonad'.

So there you have it, a Nonadic CPU!

I'm not trying to build something groundbreaking or high performance, I am just on a discovery journey about the various stages computers go through when being created - from gates to gaming.

I've been posting updates to this project on my newsletter, The Mad Ned Memo . But because I don't want to spam everyone there with a million posts about this project, I created a blog here for those few who really want to keep up with the details.

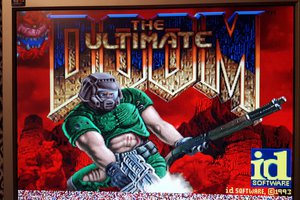

I'll try to update it as I go along this journey. My goal would be to get some substantial thing running on my CPU. Like a game, perhaps. This involves not just the CPU design but other I/O aspects like video and some input processing, and of course a lot of software stuff. We'll see how far I get!

Mad Ned

Mad Ned

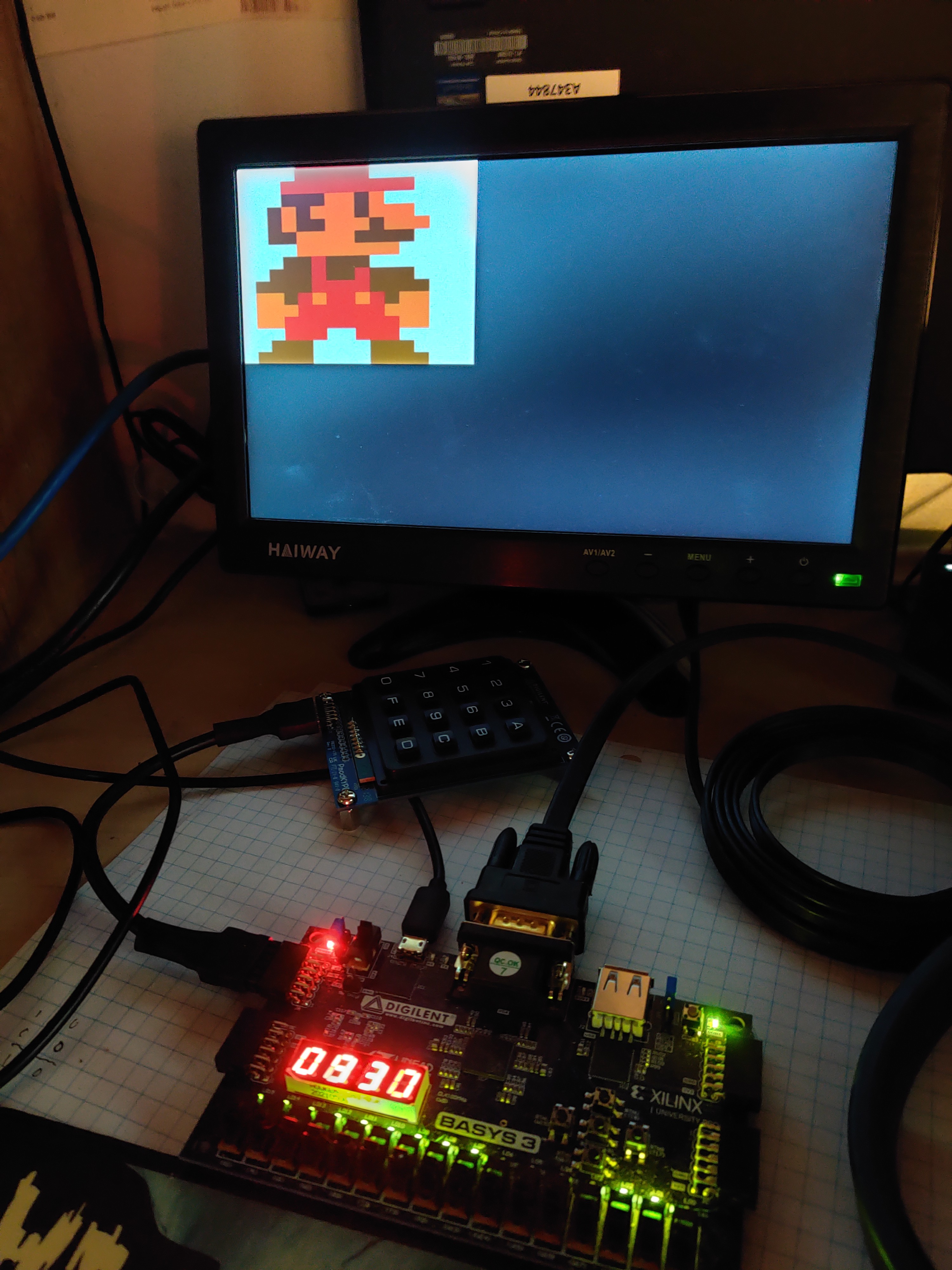

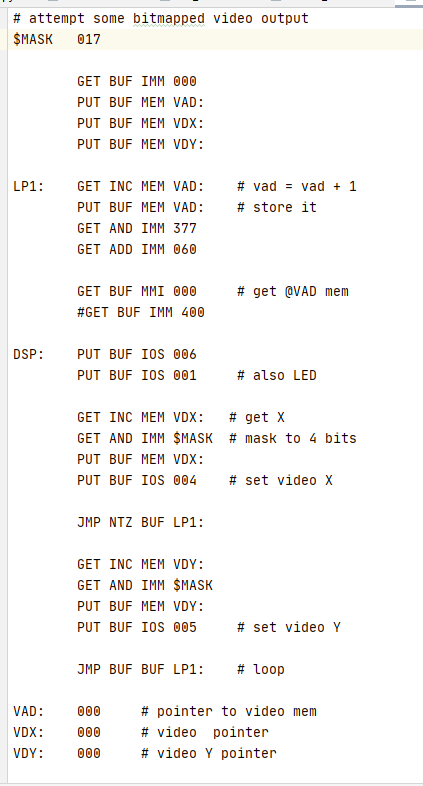

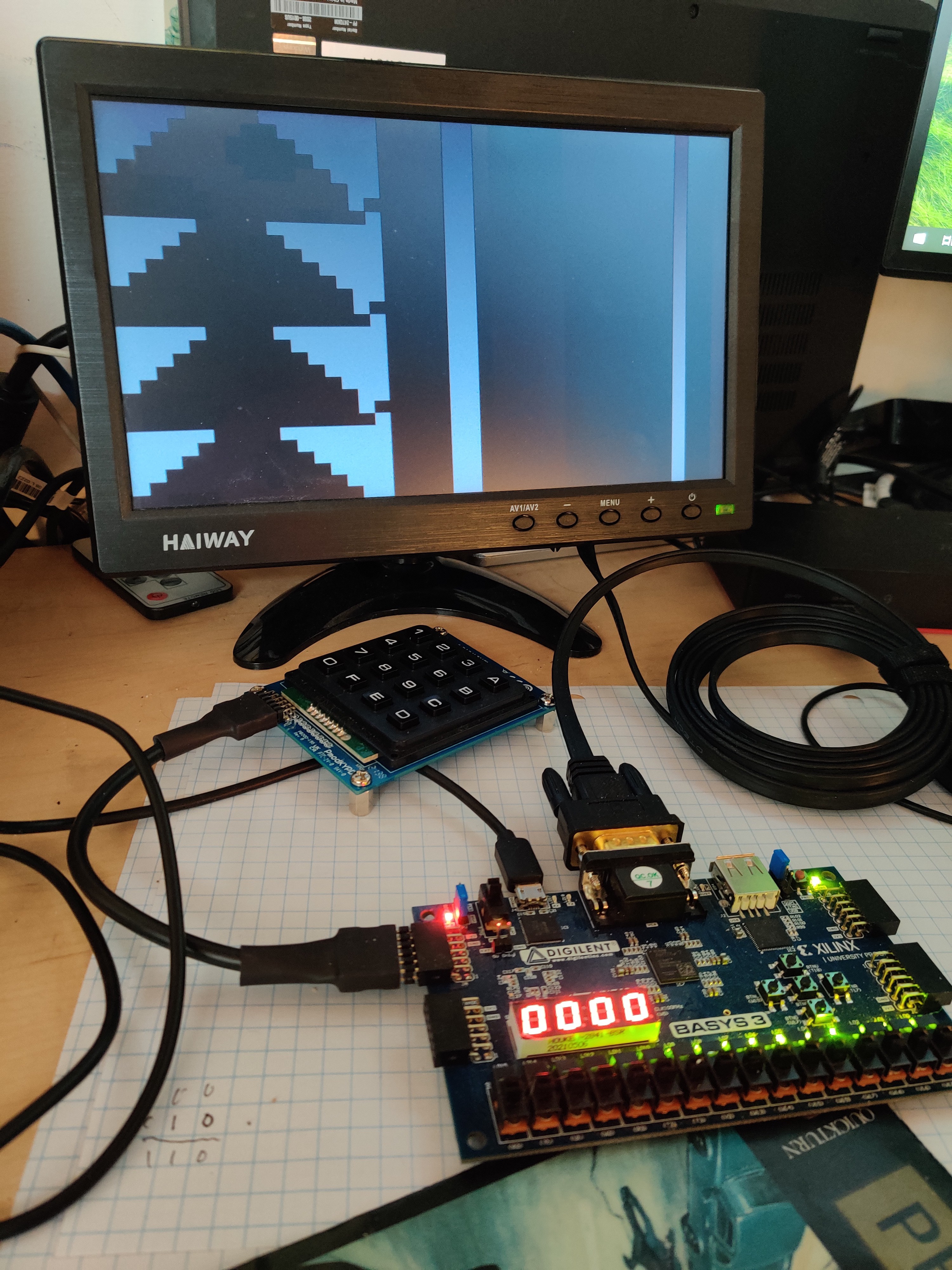

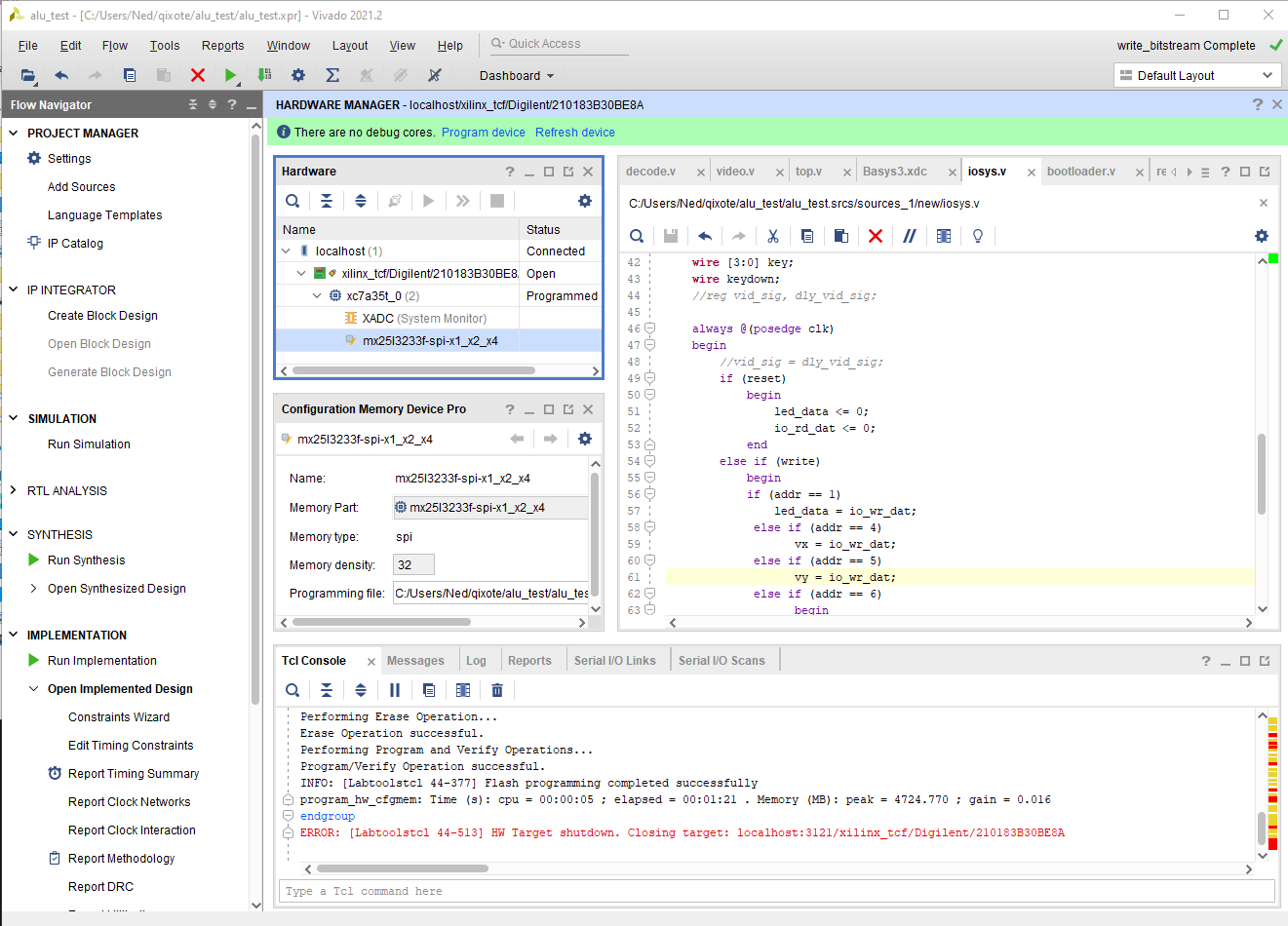

It's wrong in almost every way, but I'm excited to see my QIXOTE-1 processor executing a program that produces video (VGA) images! The system now includes a video buffer 512x512 9-bit color pixels (noxels?) That can be written to via memory-mapped I/O from a program. The video driver feeds a VGA timing circuit that produces a signal right off the BASYS 3 board.

It's wrong in almost every way, but I'm excited to see my QIXOTE-1 processor executing a program that produces video (VGA) images! The system now includes a video buffer 512x512 9-bit color pixels (noxels?) That can be written to via memory-mapped I/O from a program. The video driver feeds a VGA timing circuit that produces a signal right off the BASYS 3 board.

Foxchild

Foxchild

Dylan Brophy

Dylan Brophy

Blair Vidakovich

Blair Vidakovich

Matt Stock

Matt Stock

I will be following with interest. My hunch is the CPU won't be a big issue, you can make it all consistent internally, but the supporting software will pose interesting challenges. You may have to go to the next step, 16 bit words, in the host software. I think you wrote as much.