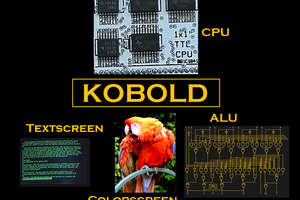

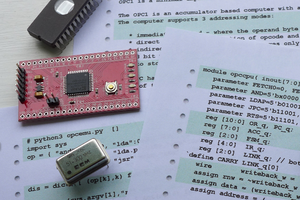

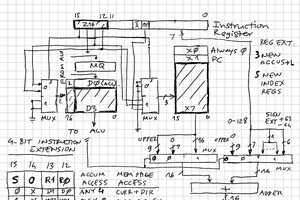

The instruction set for ECM-16/TTL homebrew CPU can be subdivided into several broad categories:

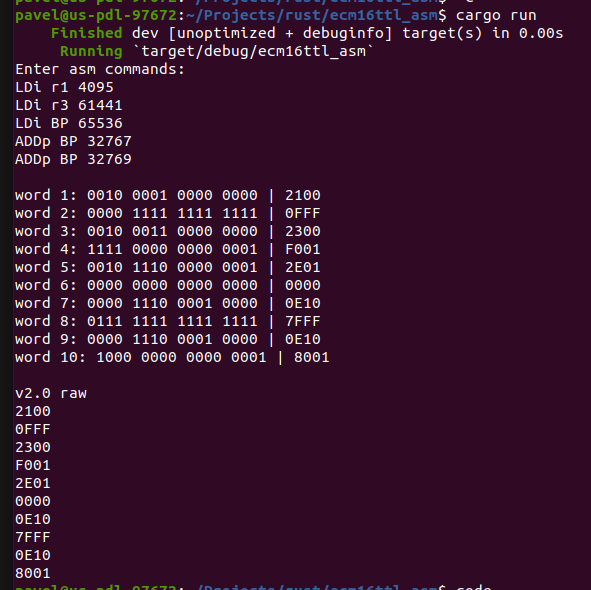

- ALU operations on General Purpose Registers

- MOVs

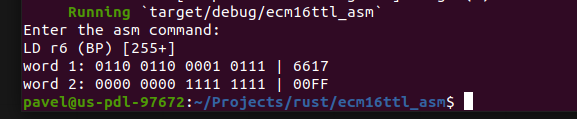

- Loads of immediate values into registers

- Loads/Stores via explicit (direct) address

- Loads/Stores via address stored in Memory Pointer + offset

- Jumps

- Arithmetic operations on Memory Pointers

- Miscellaneous operations outside above categories.

These categories are defined by State Machine branching diagram.

Pavel

Pavel

Ed S

Ed S

zpekic

zpekic