Matt Venn will host the Hack Chat on Wednesday, March 16 at noon Pacific.

Time zones got you down? Try our handy time zone converter. Reminder: this is the first Hack Chat this year after the time change in North America, so check carefully.

When it comes to electronic designs, most of us are content to make (sometimes) useful circuits using chips that were designed by someone else. That's the beauty of this game, really -- a lot of the hard work has already been done for you in the form of microcontrollers, gates, memory, amps, and timers that are all well-characterized, cheap, and readily available. Well, maybe not that last one right now...

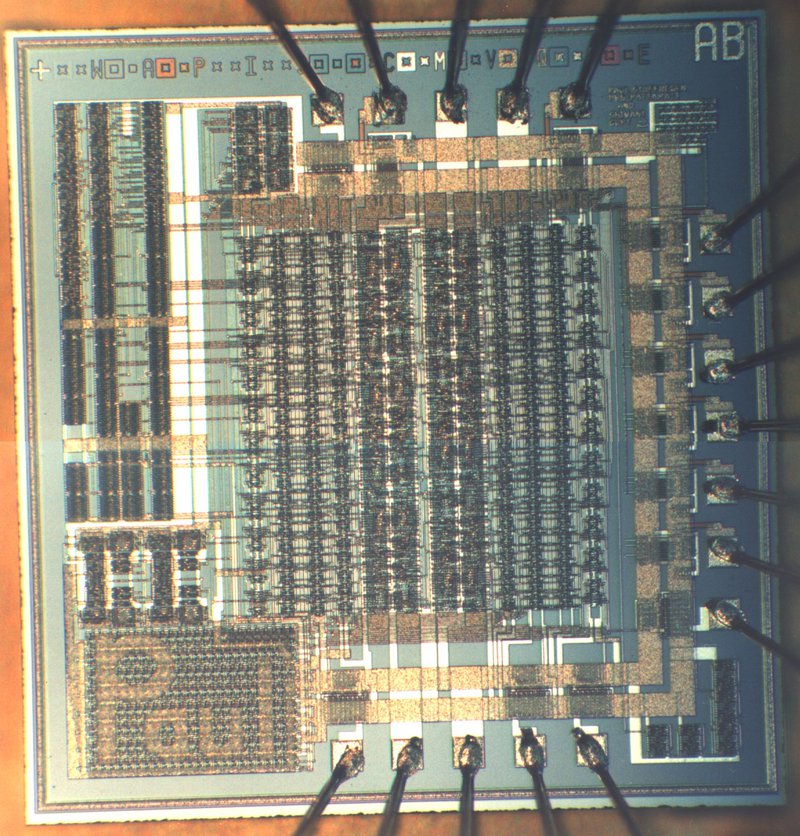

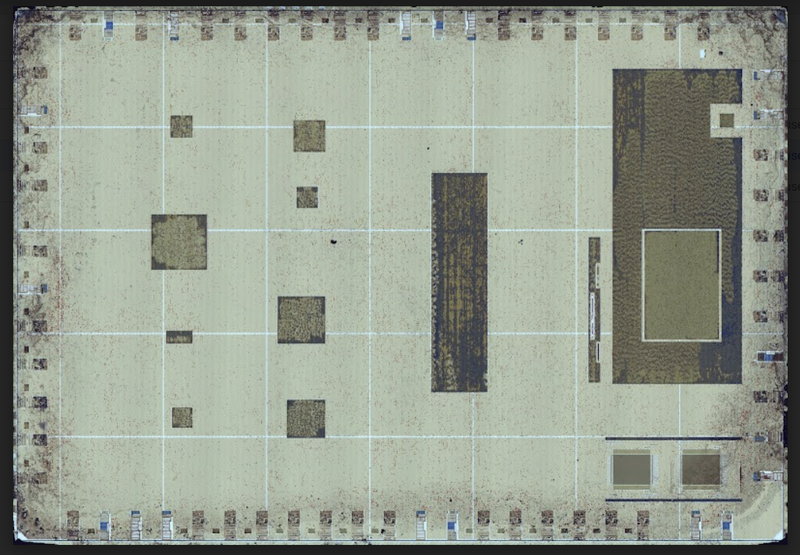

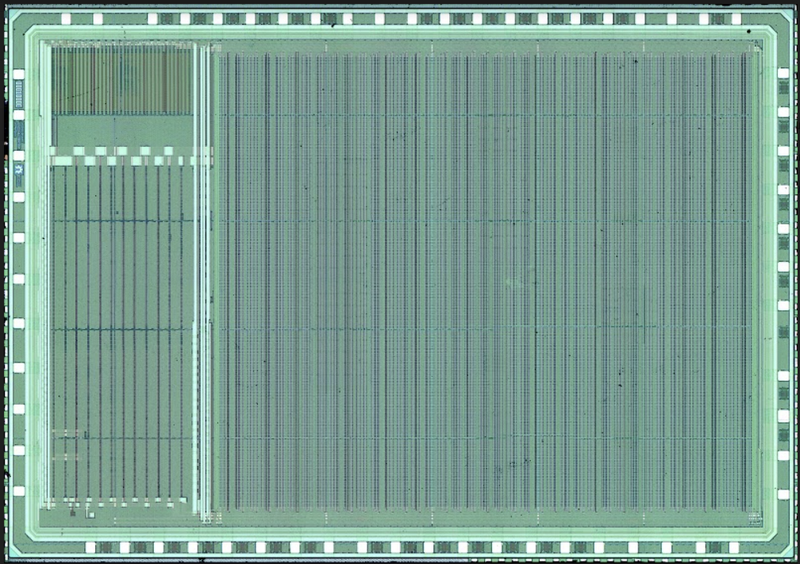

Supply chain issues notwithstanding, though, there's plenty to be said for designing your own silicon. It's not for everyone, of course, but if you need something custom, something that nobody else has ever dreamed up, then you really might want to consider rolling your own. Trouble is, most of us don't really have the tools to design something as exquisitely complicated as a silicon chip, and we don't exactly have access to a multi-billion dollar fab plant to spin up a couple when the whim strikes.

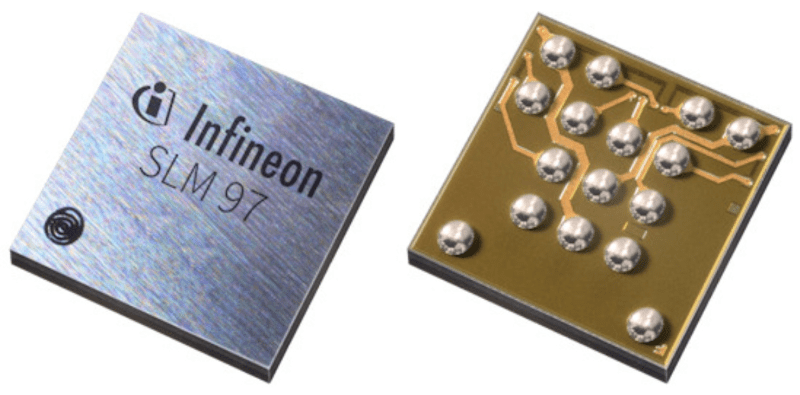

Or do we? As it turns out, we all do have access to the tools and technologies needed to turn our designs into silicon. We just need a little guidance, like that offered by Matt Venn and his "Zero to ASIC" course. You'll no doubt recall that Matt made appearances at both the 2020 and the 2021 Remoticons to talk about his efforts, and his recent partial success with his application-specific integrated circuit (ASIC). Now's your chance to ask Matt questions about the process, what the course is all about, and how you can make your silicon dreams come true.