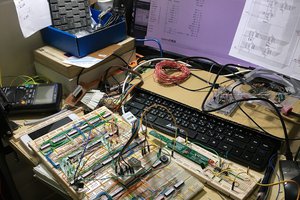

The AOZORA project aims to implement a 16-bit computer with mainly 74-series TTL ICs on solderless breadboards, providing an open and easy platform for educational purposes.

"AOZORA" is an acronym for "Allgemeine Ordentliche SOgenannte RechnenAnlage", which means "general-purpose well-organized so-called computing machinery". AOZORA may also be transcribed as Japanese Romaji to Kanji (漢字, Chinese characters) "青空".

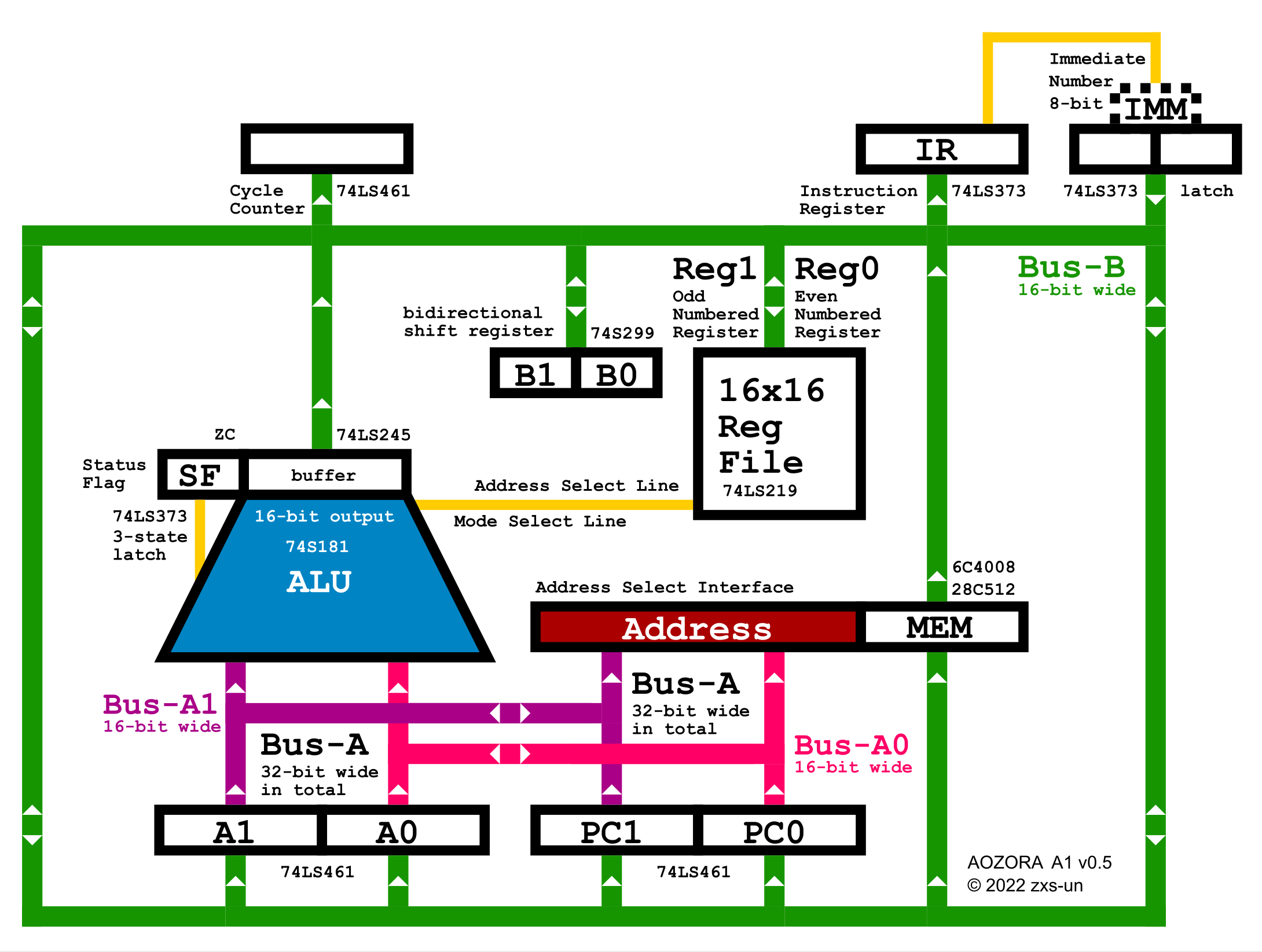

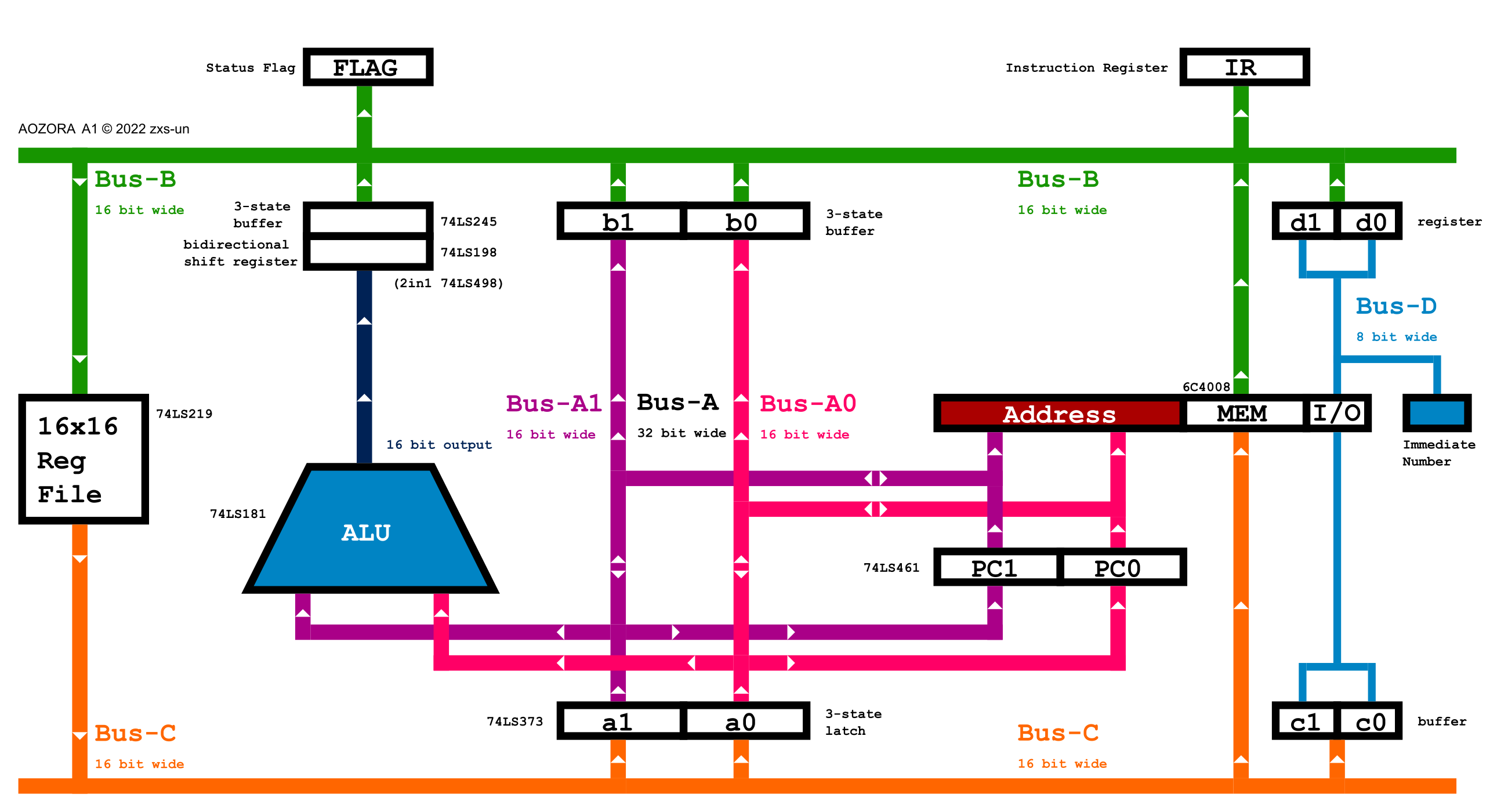

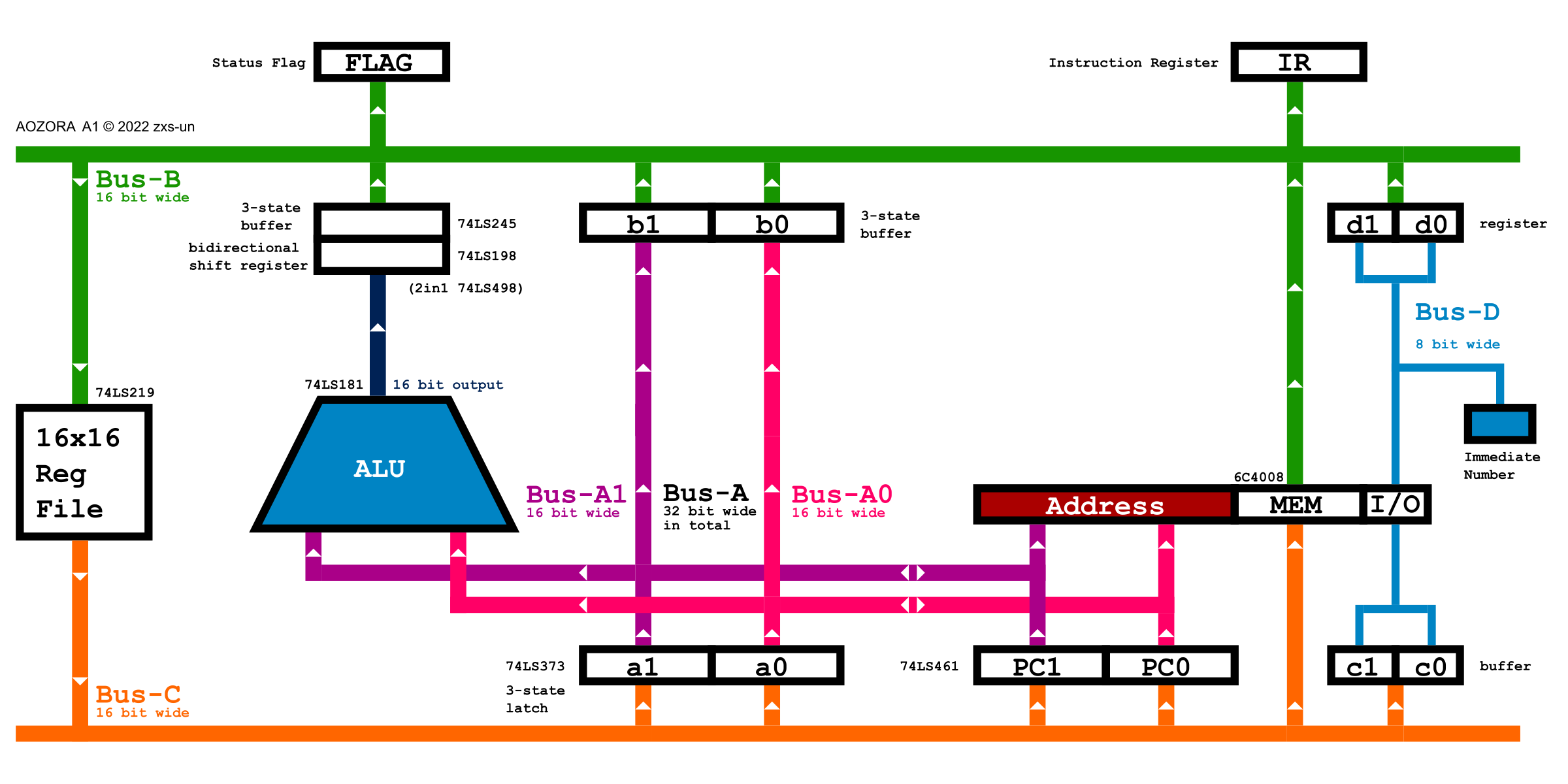

A1 features:

- Load-Store Architecture

- 16 general-purpose registers

- 16-bit word length

- 32-bit address space (4G)

zxs-un

zxs-un

ARITH-MATIC

ARITH-MATIC

Ingo S.

Ingo S.

pondahai

pondahai

Samuel A. Falvo II

Samuel A. Falvo II