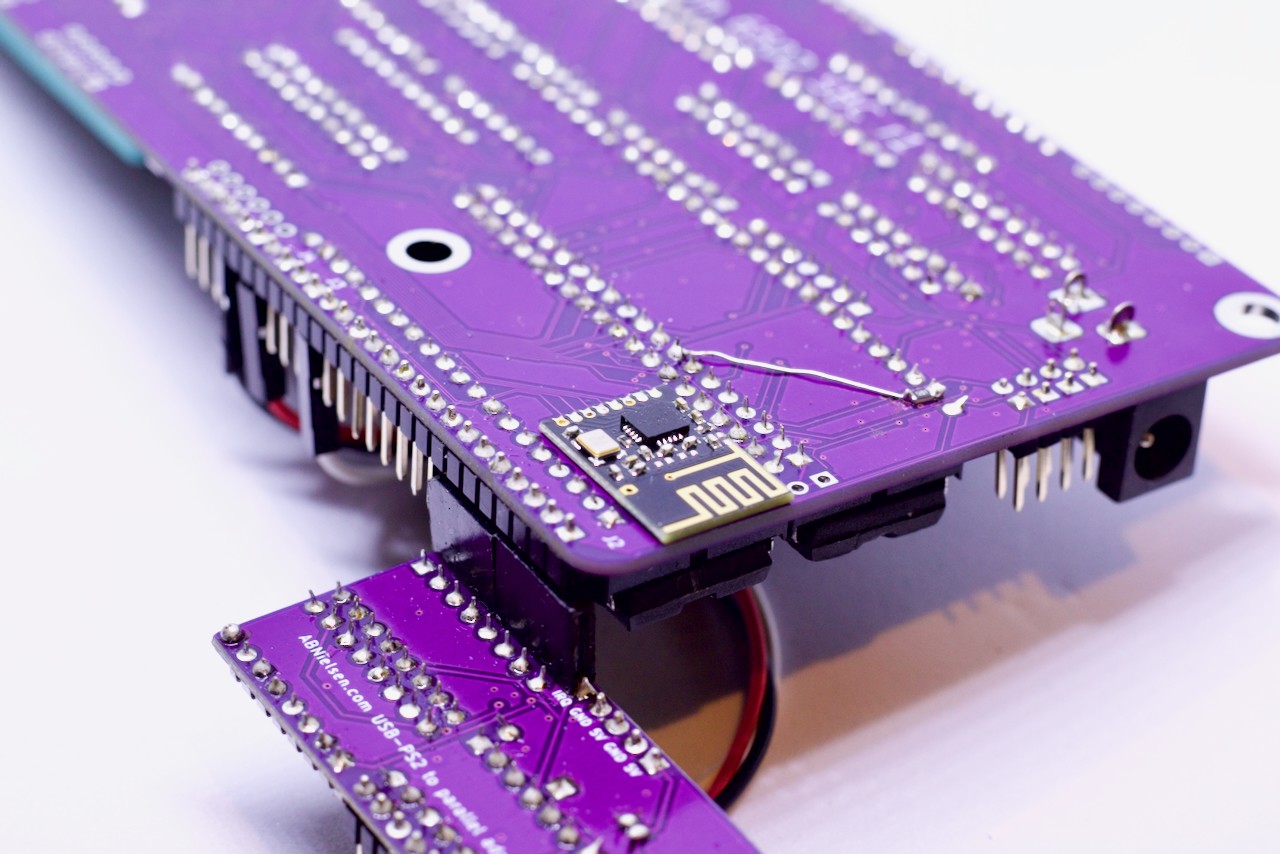

The cute little jumper wire in the photo below has a 1200 Ohm resistor on one end and pulls phi2 high.

You see, when I was testing R1 with different 6502's most of them suddenly worked horribly, RAM got corrupted, screen was displaying garbage, and most of the time it would just crash. When I put my scope on PHI2 the news was not good. Instead of showing a nice 2 MHz square wave, what I got was basically a shark fin pattern. A slow rise, up to about 4.7 Volts and then a reasonably fast drop.

When I asked on the 6502.org forum, the guesses ranged from "it's normal" to "you might have a defective internal pullup" - of course with a detour to "something is loading it"-town.

It turns out three out of the four 6502's I tested were NMOS and the one that worked was a CMOS variant. Since they were all sanded and relabeled(I wish they would stop that stupid practice! Especially for chips where a particular model may have sentimental value) I had no way of knowing.

Somewhere along the way I managed to get my glue timing skewed just enough that it would only work on a CMOS 65c02 with nice sharp edges for phi2 - and adding the extra 25ns from the slow rise, even though I ran it through a schmitt trigger inverter, completely broke the RAM write timing.

The solution here turned out to be adding a little bit of help to the internal phi2 pullup resistors with an external pullup. Anything over 1k2 Ohms didn't make much of a difference, so that's what I chose, since we want as little current flowing as possible when phi2 is low.

It still doesn't give me the nice sharp phi2 of the CMOS variant, but it certainly saves enough precious nanoseconds that the whole board - which is supposed to be NMOS compatible - works with both types.

For a later revision this will certainly get it's own pad so you don't have to jumper a resistor, but better yet would be to fix the issue of phi0 vs phi2 timing.

For now - this pretty little thing is required for correct NMOS operation.

Anders Nielsen

Anders Nielsen

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.