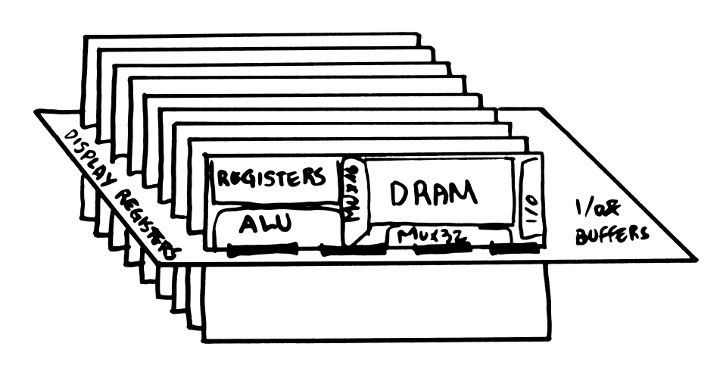

For the "computational unit", I have designed this structure:

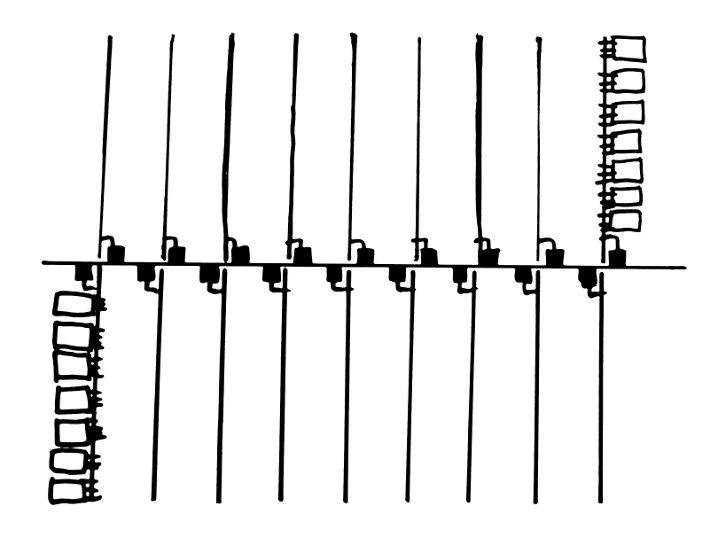

The spacing between boards is approx. 1 inch so 18 boards will make a 18 inches wide boards ! (round that to 20 inches for the extra space). It is possible to reduce this to about 10 or 12 inches by using both sides of the main backplane :

The bitslice boards are about 10cm tall and plug into the backplane with dual-row, 90° 0.1" pin headers.

Each bitslice has separate blocks : register set, ALU, memory. They are interconnected on the backplane to enable or modify certain functions:

- of the 18 ALUs, only 16 are used

- all the bitplane boards are identical but some are connected to make them work as parity bits

The memory is designed for 256 and 512 words. The "512" version is just an add-on and the bitplanes can receive one or two modules with 256 bits (and 16 relays) each.

The I/O is another story though.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.