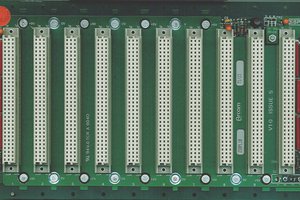

The PD32, was published in Micro Cornucopia number 32, (October/November 1986), page 6.

Supports the 32016. Has 512k bytes of DRAM modules.

It is a complete processor board.

It has no bus interface.

It communicates through an 8-bit bus, but not a latch. I don't know how that works - do they wait state unti the other side has read the bus. The article talks about interfacing to the Z80 bus.

I'd prefer to get it talking to the STEbus or an FTDI USB FIFO module.

It comes with all the PAL equations and software to implement UNIX.

I could not find the DRAM controller chips on eBay, so I presume they are effectively extinct in the wild.

The design could be adapted to use modern SRAM chips. A pair of 512k x 8 bit chips would provide double the original RAM.

The byte-wide communications interface could be adapted to use Jonathan Harston's single-channel Tube API, and thus allow Acorn PANOS to run. But that's a job for people with more time than me.

I'm not that motivated to make a PD32, my hobby is mainly capturing electronic design details for posterity and people who want to make them. I don't have time to more than a few pet projects, nor do I have space to store stuff.

I had a quick go at assembling the ROM source and the PAL equations but failed. They need major syntax edits and checking.

Keith

Keith

Tom

Tom

Kaili Hill

Kaili Hill

Interested! I see most of the things I was going to mention over on the RetroBrew forum, except for Andrew Voropay's wiki page (http://wiki.sensi.org/dokuwiki/doku.php?id=ns32ktoolchain) about using old versions of GCC and binutils for cross-compiling.