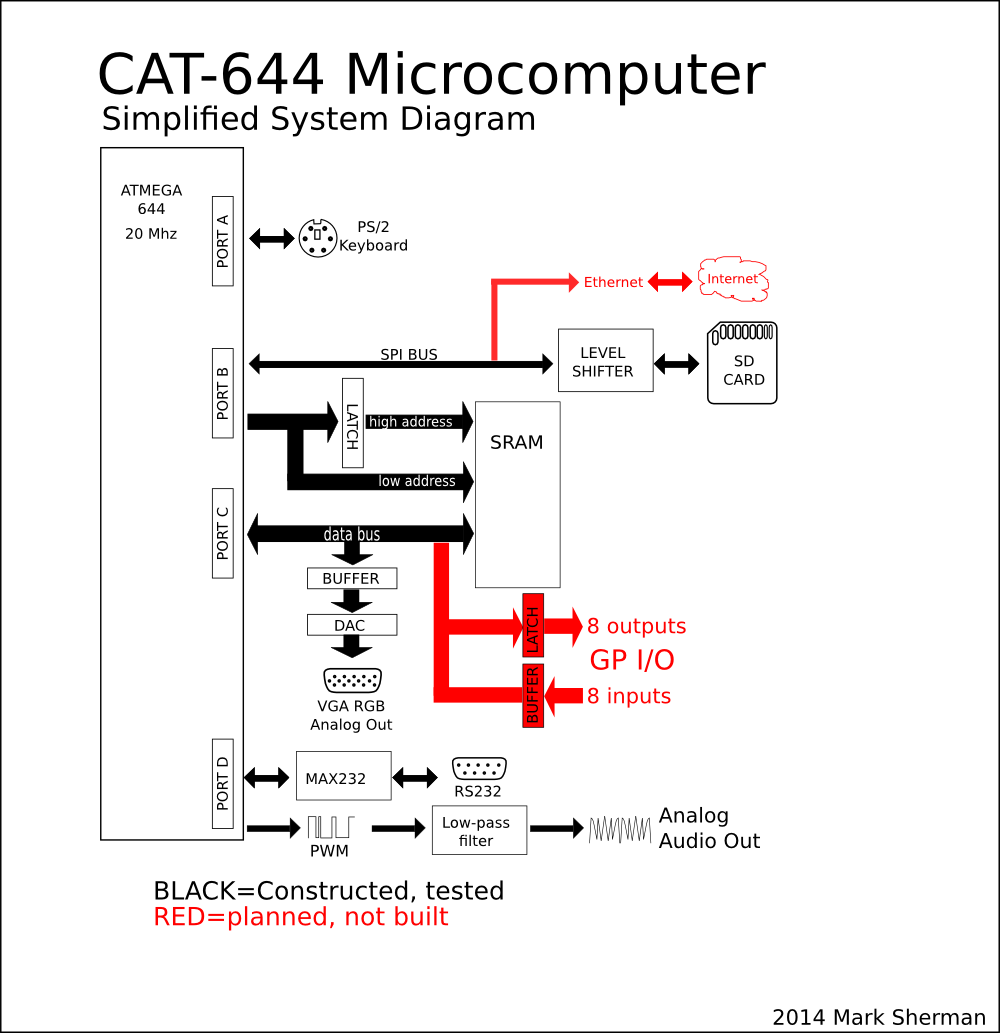

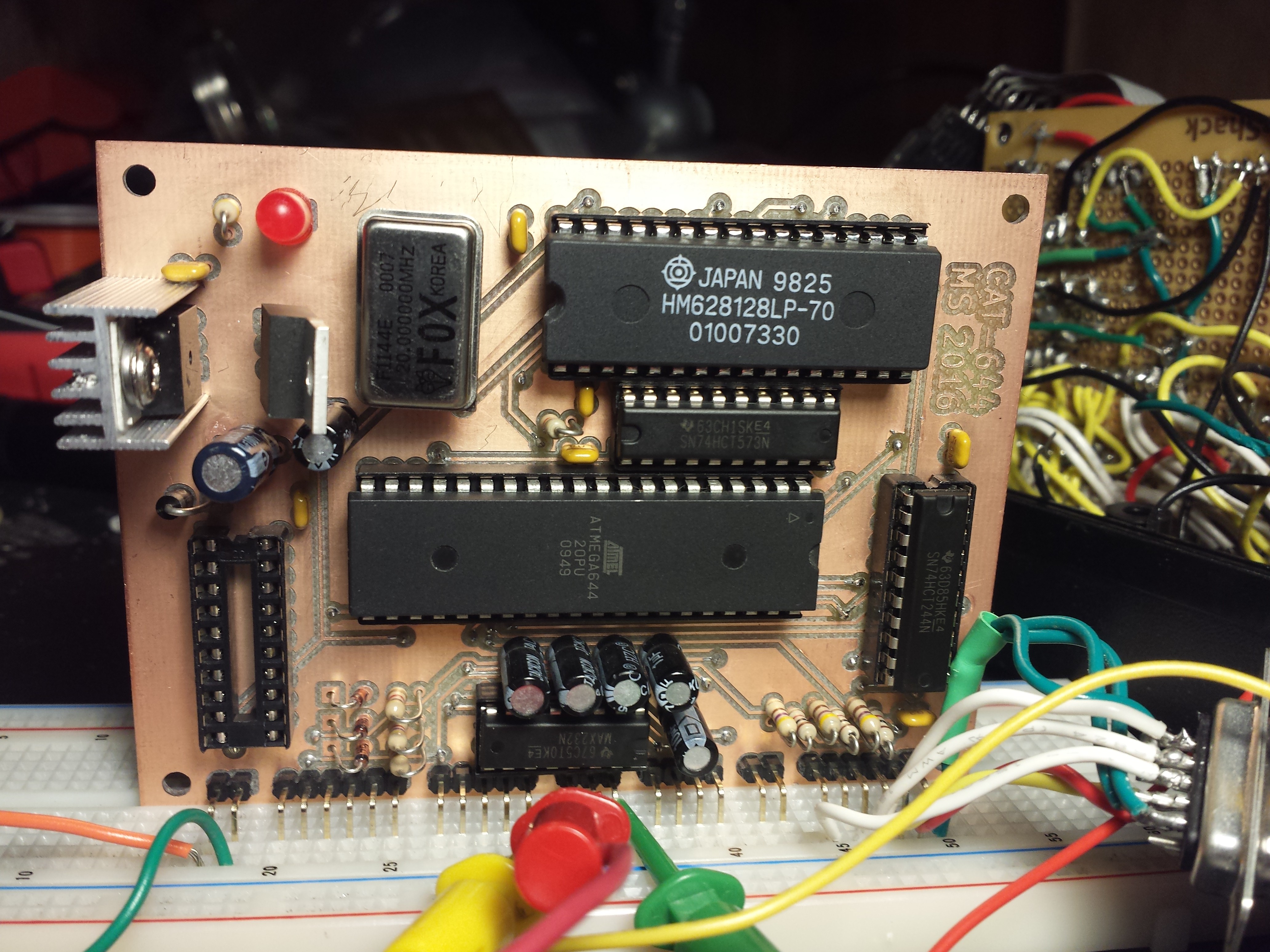

Hardware Introduction

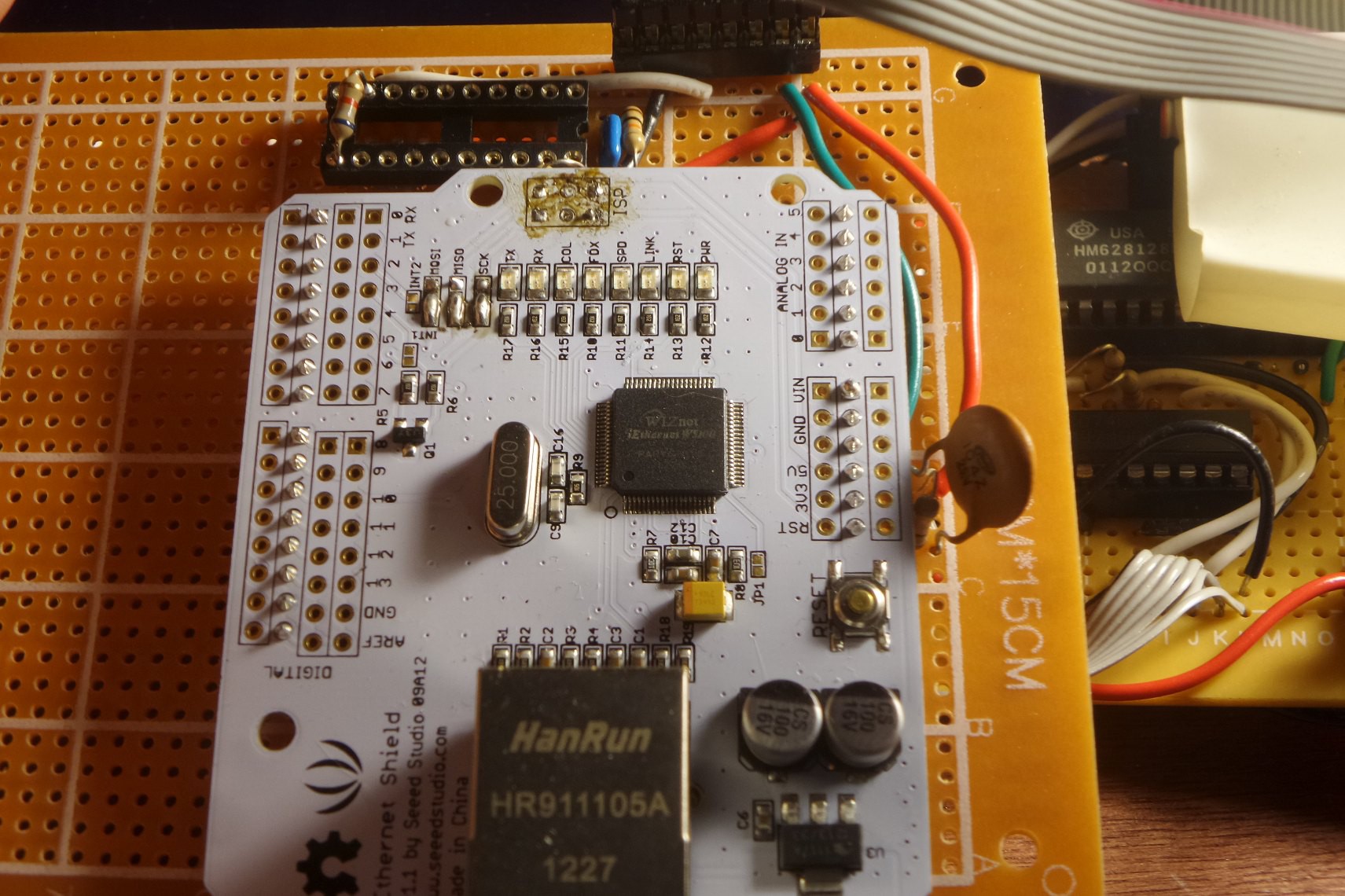

The CAT-644, is a simple computer using a 20 MHz ATMega644 microcontroller as its CPU. I am using the DIP-40 package, making it breadboard and hobbyist friendly. Large sections of this project can be built and run entirely on a breadboard, without any soldering. The ATMega644 offers four 8-bit GPIO ports, with each pin configurable as an input (with or without internal pullup resistors) or an output. Many pins also have special hardware functions that can be enabled.

This is the current use for each pin in the CAT-644:

- PORTA

- A.0 through A.2 are currently unused! The possibilities are endless!

- A.3 is the SD card enable line (explained in Disk section)

- A.4 is the VGA DAC enabled line (explained in Video section)

- A.5 is the Address 16 line (explained in RAM section)

- A.6 is PS/2 data signal (explained in Keyboard section)

- A.7 is the PS/2 clk signal

- PORTB

- B.0 through B.7 are used as an 8-bit address bus for memory operations

- Alternatively, pins B.7, B.6 and B.5 make up the SPI bus. This function is used when talking to the SD card.

- B.4 and B.3 are outputs that can be controlled by 'Timer 0' of the AVR. The timer counts clock cycles, and when the right value comes up, these pins can be controlled w/out software intervention. This is used to make the address bus count faster than the CPU would normally allow for. (explained in Video section)

- PORTC

- B.0 through B.7 are used for the data bus while doing RAM operations.

- Some PORTC pins are also used for JTAG. I am not using JTAG, but mention it, as it just be explicitly disabled to avoid it from interfering with normal PORTC operation.

- PORTD

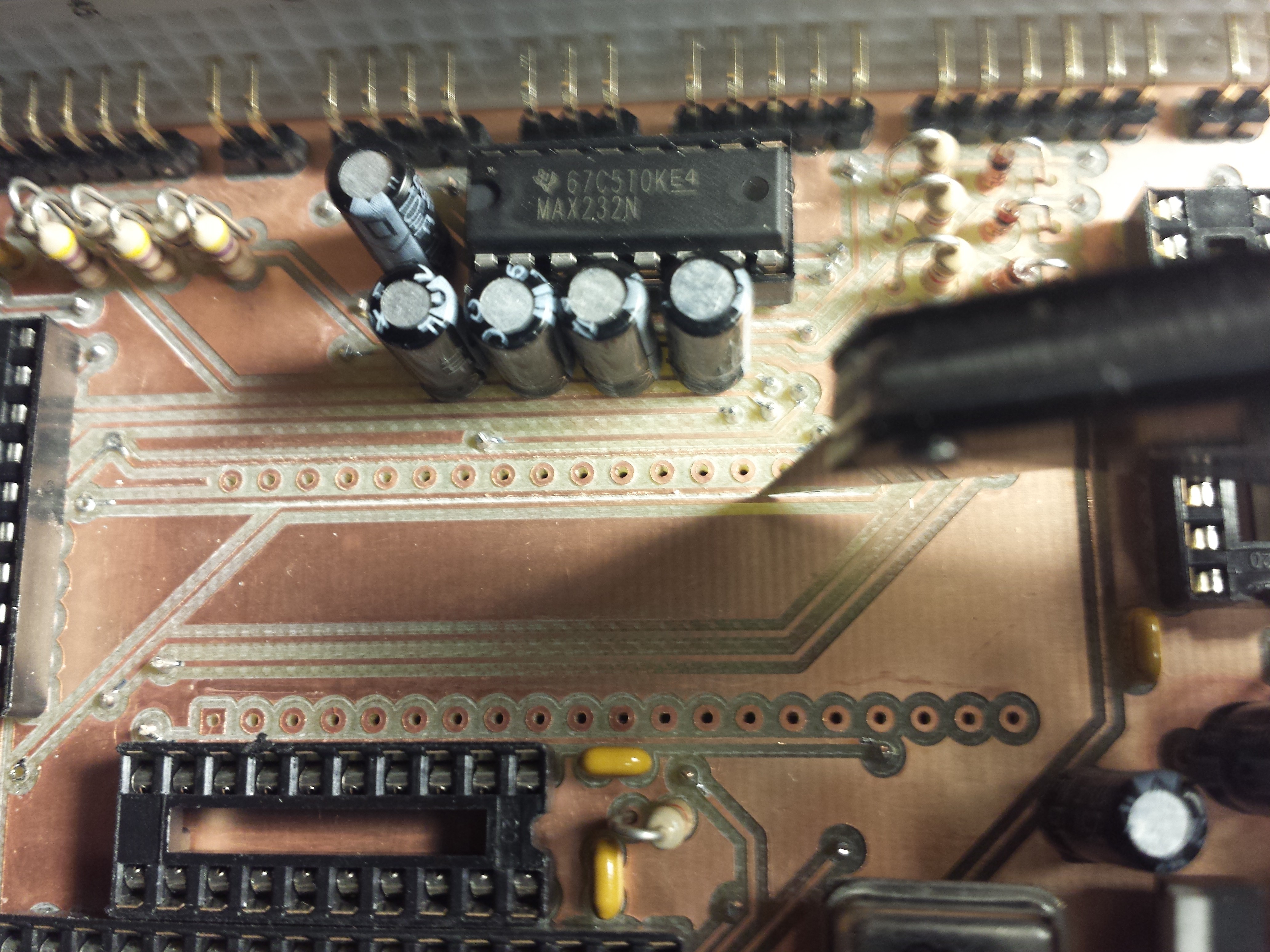

- D.1, D.0 RS-232 port (see Serial section)

- D.2 Ram output enable

- D.3 Ram page latch (see RAM section)

- D.4 VGA Vsync

- D.5 VGA Hsync. This is also a timer 1 output pin.

- D.6 RAM Write Enable

- D.7 Timer 2 output. This is used to generate PWM audio signals. (See Sound section)

Mars

Mars

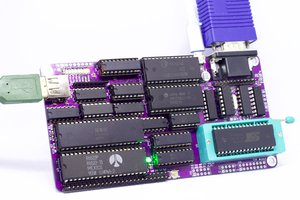

Yep, the shorted traces were in the most annoying place possible: under the socket. Separating these two traces are on the top of the kicad todo list.

Yep, the shorted traces were in the most annoying place possible: under the socket. Separating these two traces are on the top of the kicad todo list.

6502Nerd

6502Nerd

Anders Nielsen

Anders Nielsen

Keith

Keith

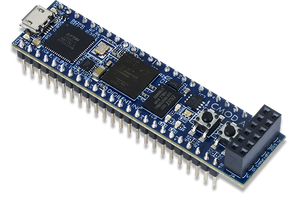

You can also try to overclock the MCU to 25MHz to have true VGA pixel clock. Perhaps you have seen similar project UzeBox http://belogic.com/uzebox/hardware.htm where ATMega644 works at 28 Mhz.