We made the leap from 16 bits to 32 bits! At the last update, we had our RISCy 16-bit OPC6 running on various FPGAs and also in emulation on Raspberry Pi. It's a word-addressed machine, with instructions of one or two words, such that a register, or an operand, is big enough for an address. Limited to 64k words, but still with 3 HLLs to program it with: C, BCPL, PLASMA. We also had a single-stepping monitor program for it, and we'd run it both standalone and as a second processor to Acorn's 6502-based BBC Micro.

To compute ever larger numbers of digits of Pi, or more generally just to have more available memory, and to make arithmetic just a bit easier on large values, we cooked up a 32-bit version - welcome to the OPC7!

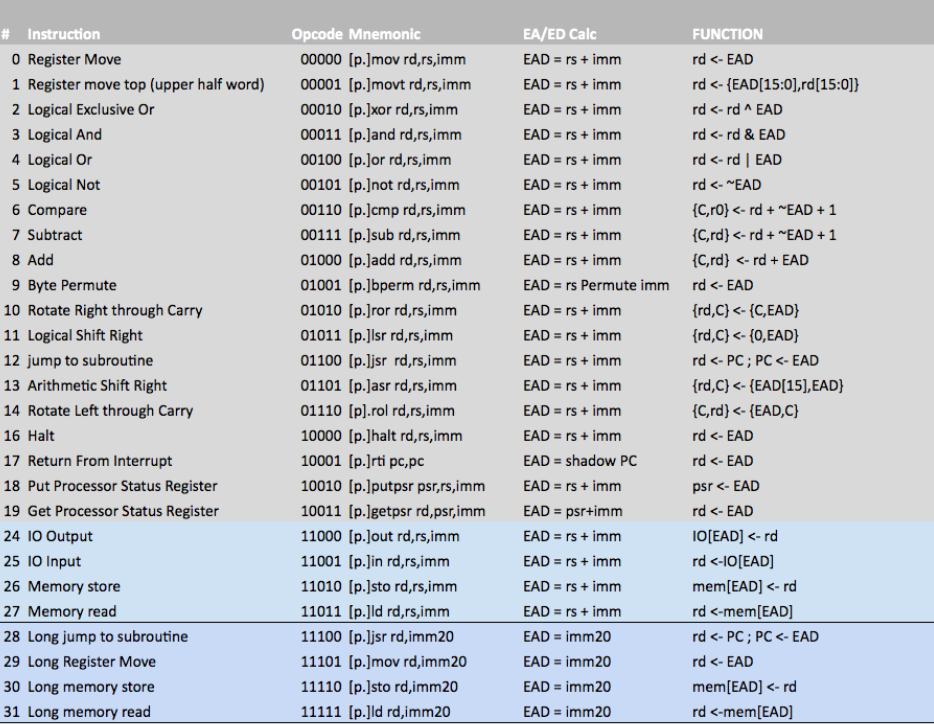

With 32 bits of instruction, we use 3 for predication and 5 for the opcode, leaving 4+4 for the registers and 16 bits for an immediate. Because the immediate is no longer word-sized, we added a Byte Permute instruction and a Move Top. We also added four instructions with a 20 bit immediate, reusing the source register field. We added a Software Interrupt mechanism for OS calls and the like. As before, short branches and relative jumps are done by adding to the PC, and the subroutine call uses a link register - there are now no push and pop instructions.

Ed S

Ed S

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.