CPU features

- 32b design

- 16 registers including 3 special registers

- Addressing up to 2^{24} words

- Work up to 50MHz

- 16 interrupt vectors

Peripherals

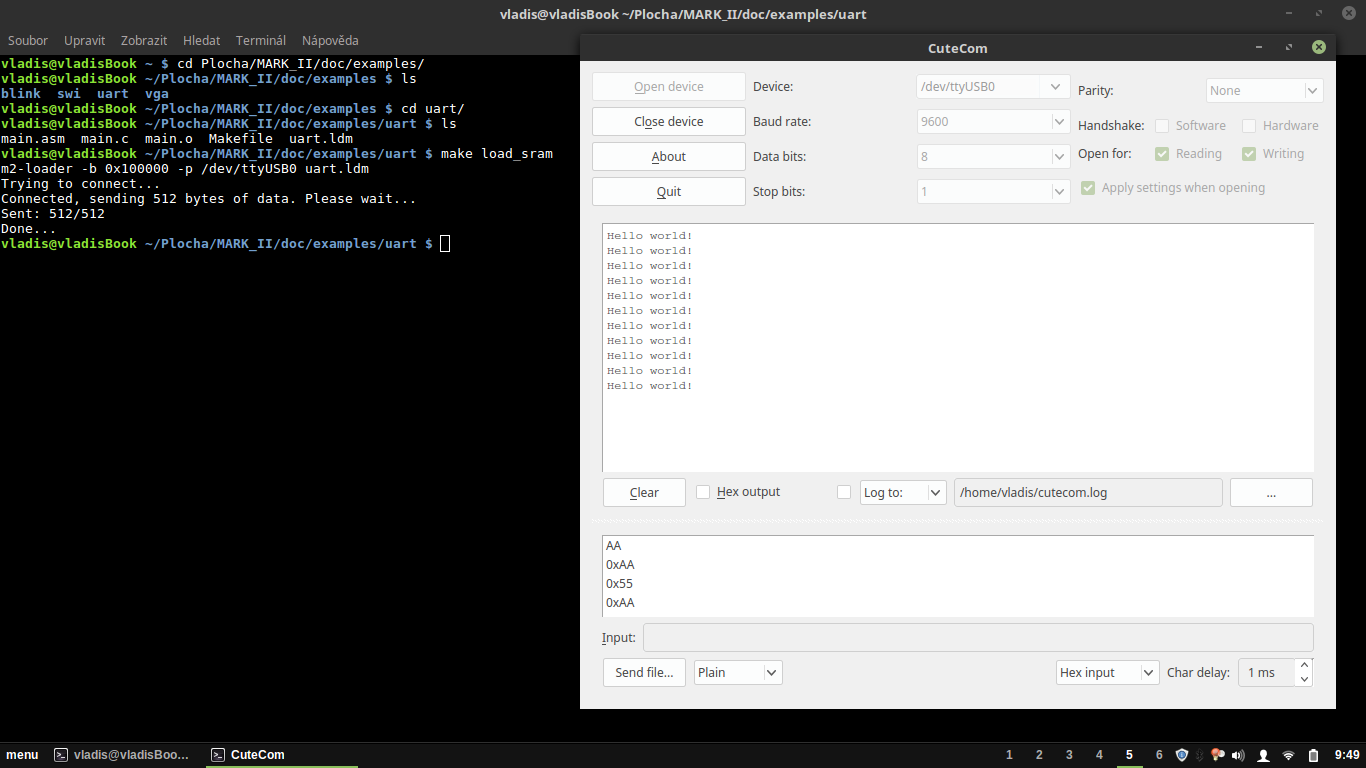

- UARTs - full duplex with configurable baud rate

- Timers - with interrupts and PWM outputs

- VGA driver - text mode 80x30 characters with 16 colors

- PS2 driver - for keyboard

- GPIO

- Memories

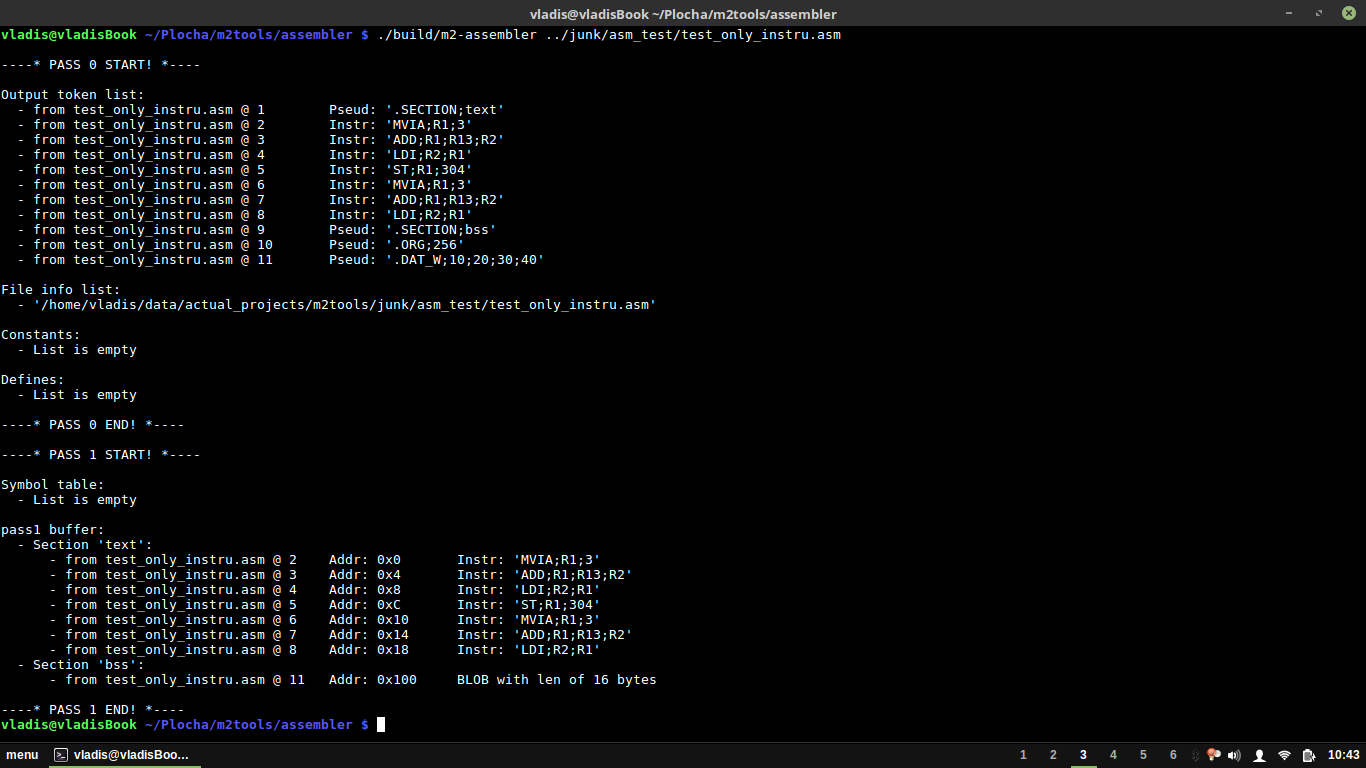

Toolchain

- C compiler

- Some C libraries

- Assembler

- Linker

- Emulator

- Disassembler

- Bootloader

Vladislav Mlejnecký

Vladislav Mlejnecký

Noah Wood

Noah Wood

Matt Stock

Matt Stock

john lemme

john lemme

jaromir.sukuba

jaromir.sukuba

I like it!

Have you seen my A2Z project?

https://hackaday.io/project/18206

The CPU itself is much simpler than yours, but I have developed a fully usable machine with graphics, mass storage, filesystem, etc... Everything is home made, including the language, the compiler, the instruction set, etc...