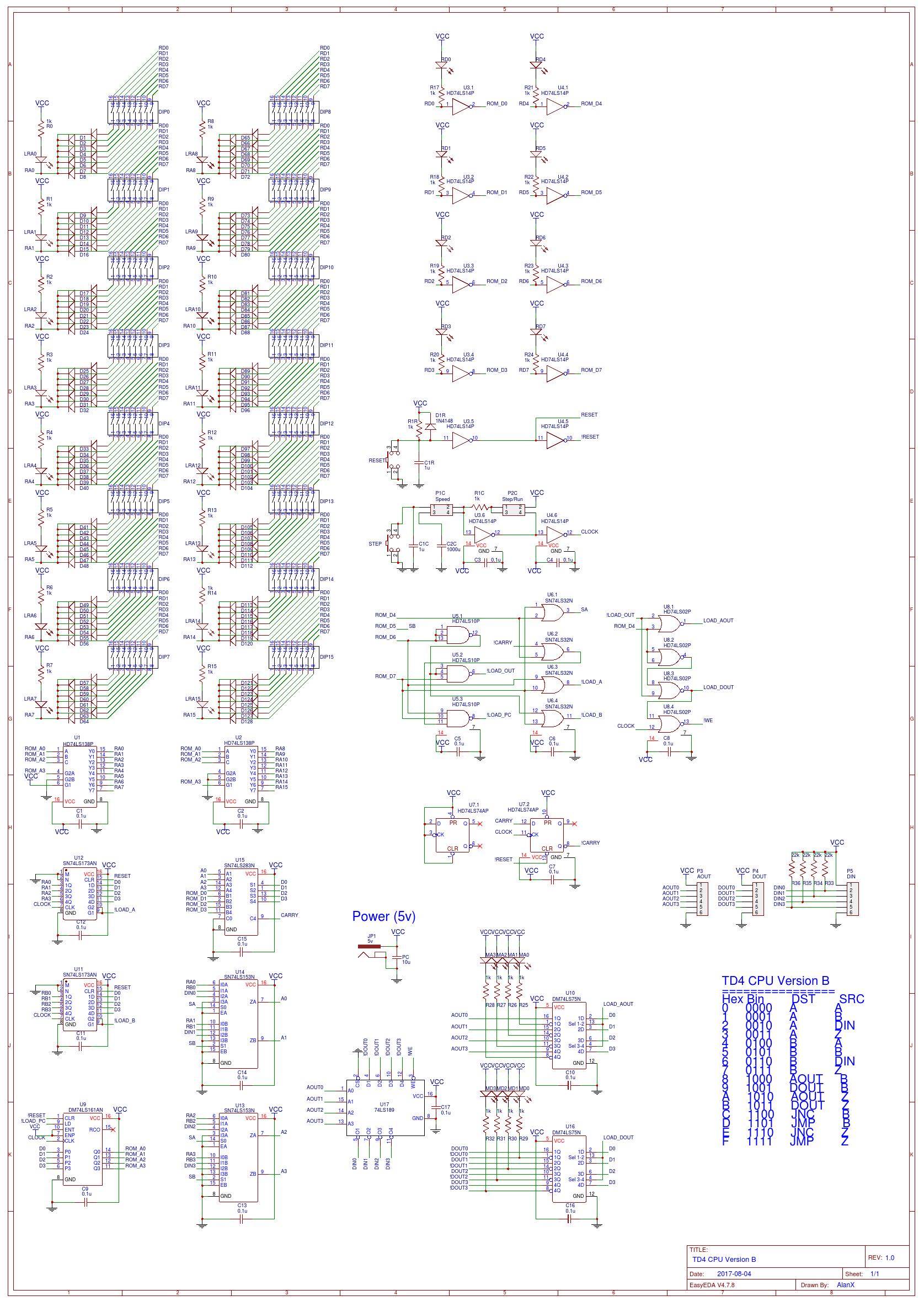

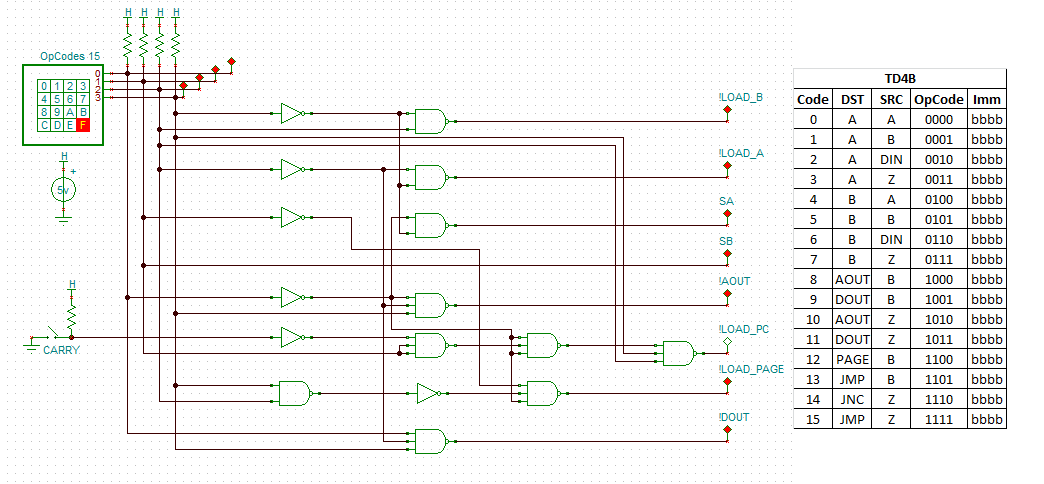

TD4 CPU Version B

Here id the full schematic

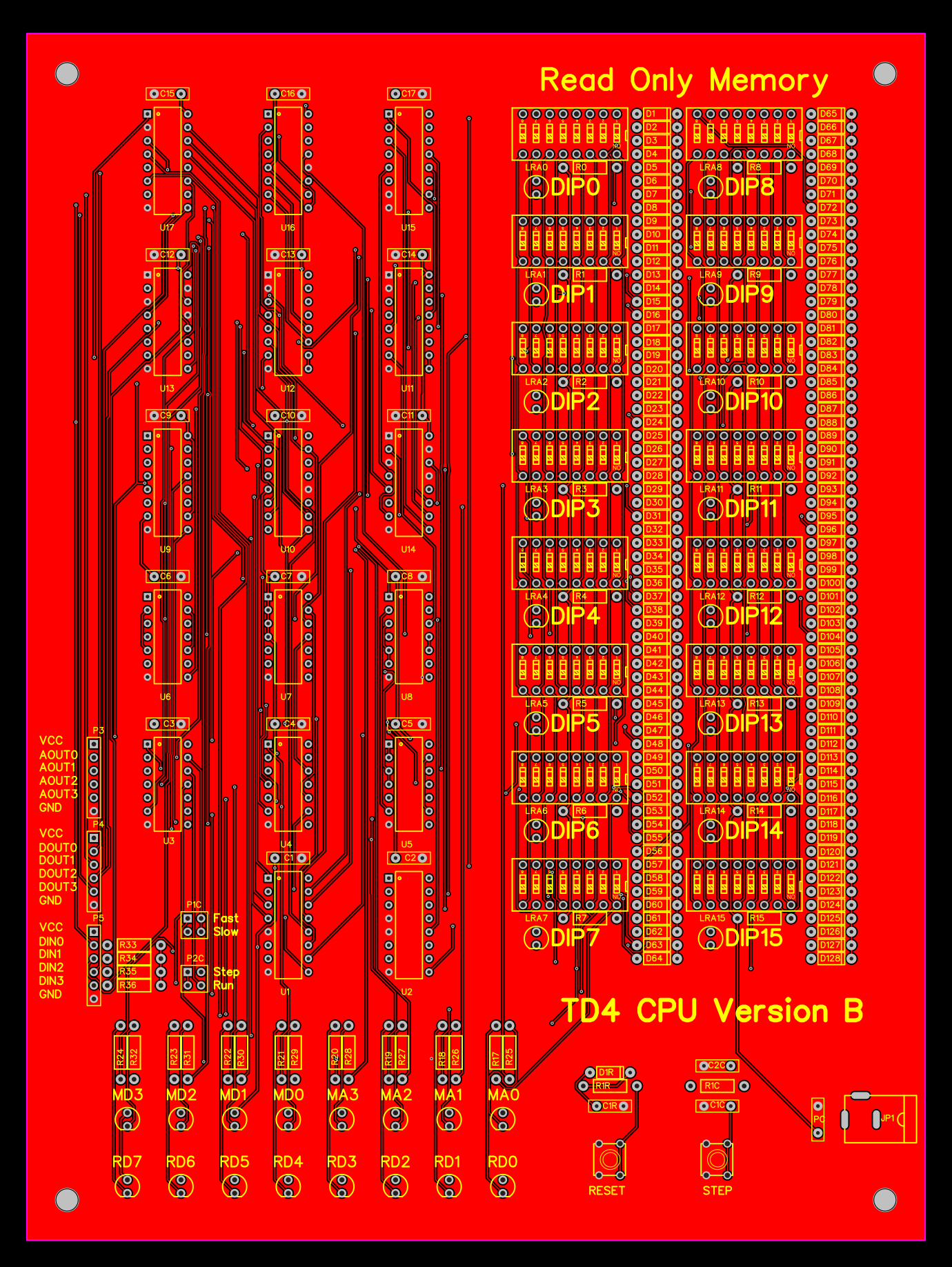

And the PCB:

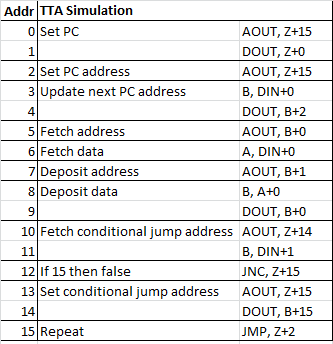

Simulating A TTA

A TTA is a Transport Triggered Architecture (i.e. a single instruction move only CPU). An example is my Weird CPU.

Why simulate TTA? It is a good test for a CPU, can it simulate another CPU.

The TTA CPU model:

- PC Mem[15]

- JC Mem[14] (n.b. it could be JNC)

- Hardware sets Mem[14] to "15" to signal not carry.

- Other memory locations would "hide" the ALU, I/O etc.

Here is my program:

In the above I explicitly test the jump address for the not carry flag. There are other hardware/software arrangements. You could read the PC and write it back as PC+2. The carry signal would determine which of Mem[15] or Mem[14] was read.

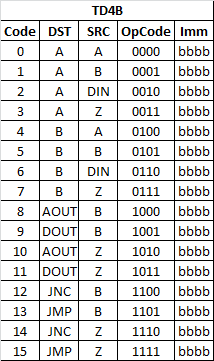

Here are the modified OpCode for reference:

So pretty cool for a 4 bit CPU. The power of this CPU is the automatic adding of immediate data with every OpCode, without it it would be dead.

Expanding the TD4B

There are two basic approaches:

- Increase the 4 bus to 8 bit but keep the 4 bit OpCode.

- Increase the only the PC to 8 bit.

The second approach is not easy. We need to add a page register. For this we have to remap on of the OpCodes (okay you could multiplex DOUT using AOUT and get 16 registers but that would take an extra instruction each time). We could remap JNC, B to Page, B. The new Page register would set the high nibble of the PC on a jump. There would still only be 16 RAM words to play with.

A Few Days Later

I coded the Page Register:

By adding three chips I have 256 bytes of program memory. I cannot program it with the CPU directly (they call it Harvard Architecture) so what to do? It needs some thought.

AlanX

agp.cooper

agp.cooper

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.