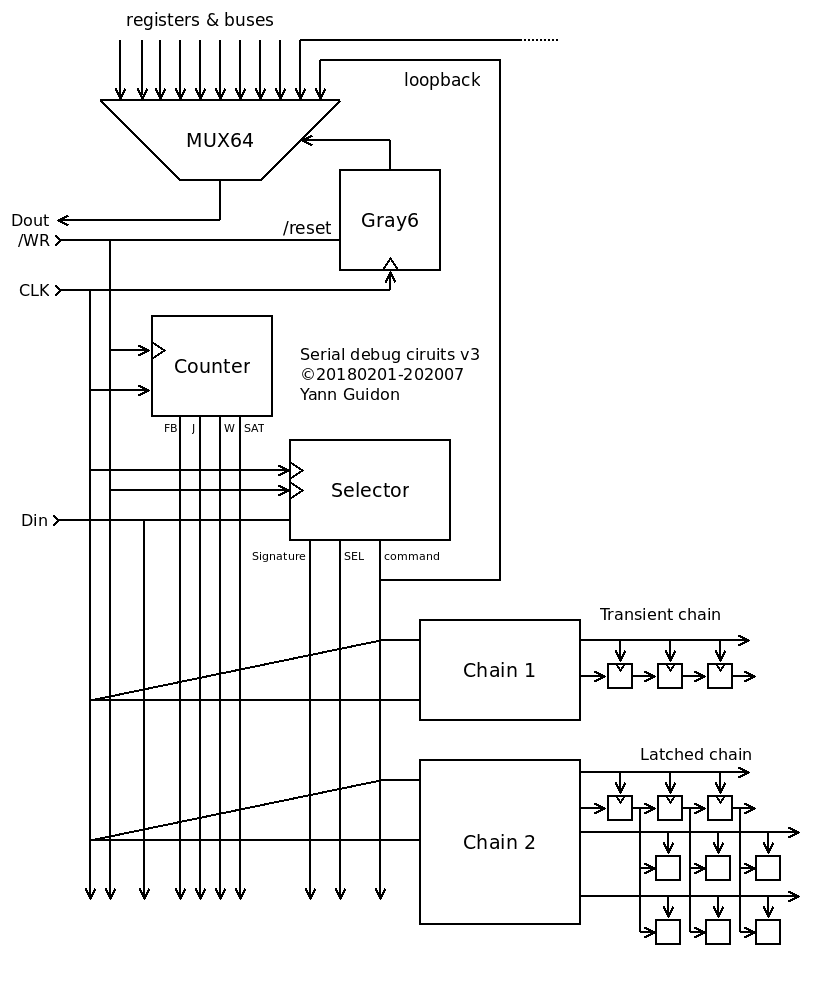

After about a week of intense work on the sub-parts, they are coming together as a TAP core module that lets us configure any structure at will.

The 4 sub-parts are combined to let me add chains of any length, either "transient" or latched. These chains can be very simple or with multiple checks, answer to arbitrary signatures or start at any position after the Selector's 16 bits.

Now comes the time to think about how to use it.

First possible example is to stream the program into the instruction SRAM :

- set /WR low (or send a NULL command if unsure)

- select the appropriate chain/function with the command '1S'

- toggle /WR high and low

- stream the 512 bytes of instructions

- send the signature byte (TBD) to validate the operation

- set /WR high

Reading back is something else, one has to go through the "normal path" : set PC to the address and read the instruction buffer. So how do you do that ?

Well first you have to stop the core, which means you also need to start or even step it : the Start/Step/Stop trinity is one of the messages that are sent to control the internal FSM with a command register. The FSM state is read back to confirm and acknowledge. This could go to the register address "F" for example.

But there is no "read the register" command. There is even better : the tree reads the values of the SND, SRI, Result and PC busses. All there is to do is inject an instruction in the decoder's input and not let the core record the result.

So far this chain looks like this :

- Instruction : 16 bits (MSB first)

- suffix1 : FSM state/message/command byte

- suffix2 : 'X' = 01011000

The Suffix1 byte can reuse the command register in the Selector unit. The instruction shift register can then be freely routed close to the decoder, and a MUX2 selects if the instruction comes from the TAP or the instruction memory.

The MUX2 is controlled by a single latch bit from the command byte : the whole shifted word is half-transient because the instruction doesn't need to be latched, but the command does.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.