People are (rightfully) confused with this project, and I understand why: it's ambitious and covers many aspects at once.

For other projects, I have split the whole project into several sub-projects, for example into an architecture ( #YASEP Yet Another Small Embedded Processor) and various implementations ( #microYasep, #Discrete YASEP...). Even for the precursor ( #YGREC16 - YG's 16bits Relay Electric Computer/ #YGREC-РЭС15-bis) I created several sub-projects ( #YGREC-Si , #YGRECmos, #YGREC-ECL... ) that clearly separate the architecture from the various technologies I wanted to explore.

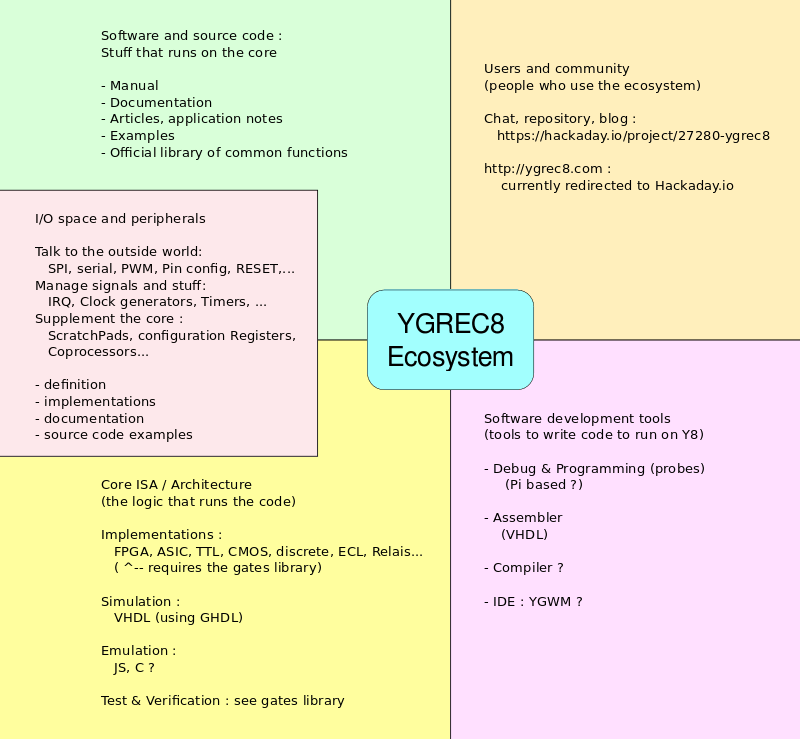

But designing a new microprocessor is more than defining an ISA and making the prototype work: it's a complex ecosystem that must be carefully crafted and every piece of the puzzle must fit right into place. I think that the following sketch give a taste of the ambition of the project :

In fact it's not so much different from the YASEP and F-CPU, except that I can go deep in the design of everything, thanks to the simplicity of the core.

The immediate use of Y8 would be as a softcore in FPGA projects where a tiny but easy-to-use and expandable microcontroller is required. However getting there also paves the way to more sophisticated cores and technologies...

I admit that at this moment, I focus mostly on the ASIC and relay implementations, which hold the whole project back and I need to progress on other fronts. However some tools (such as the #VHDL library of ProASIC3 gates) are in development and should be short-term only, but are very important for the rewrite of the core in VHDL.

Stay tuned...

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.