I tried to run my new code through Synplify (in the Libero SOC suite) and got some interesting results.

First :

I finally understand how to create and use external libraries, in particular the SLV lib worked right out of the box, after I searched for the right method. It's some of those dumb painful GUI clickodrome that looks nice during a presentation but is not possible to automate... Anyway, SLV_utils.vhdl was added smoothly.

Second :

I forgot an important "detail" about how Synplify wants its external entities : "old style"... So I had to adapt/modify a lot of lines. Nothing changed except the syntax. It's more verbose, you have to add a declaration for each block you use... But now it works.

Third :

I could check, verify and compare the behaviour of the synthesiser with various versions of one unit.

In particular I verified that the "balanced control tree" approach is beneficial compared to the dumb/usual approach. Log 25. MUX trees gets a graphical update :-)

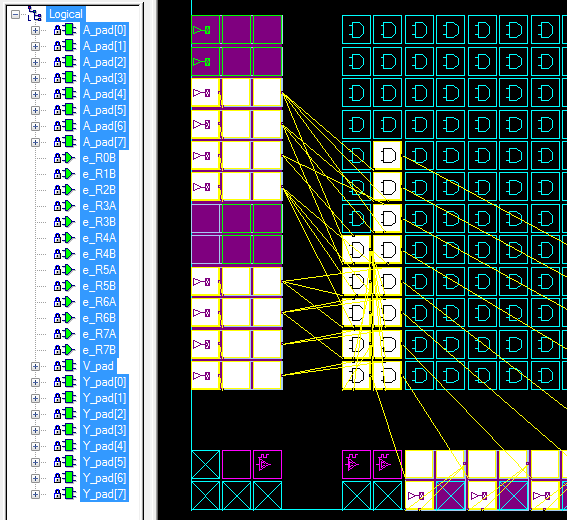

Oh and I found how to manually place & lock gates, so here is one test with INC8 :-)

The system was not able to optimise this unit more so I guess I'm not far from a great design.

Now, I just have to find how to generate these coordinates with a program and send them to the tool...

Finally :

All the modified and/or tested VHDL files have been re-integrated into the code tree with the following line :

-- SYNTHESIS OK

So it's easy to check/list all the final files with grep, and separate them from the simulation-only files :-)

I have gained more insight, refreshed my skills and proved that my method works.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.