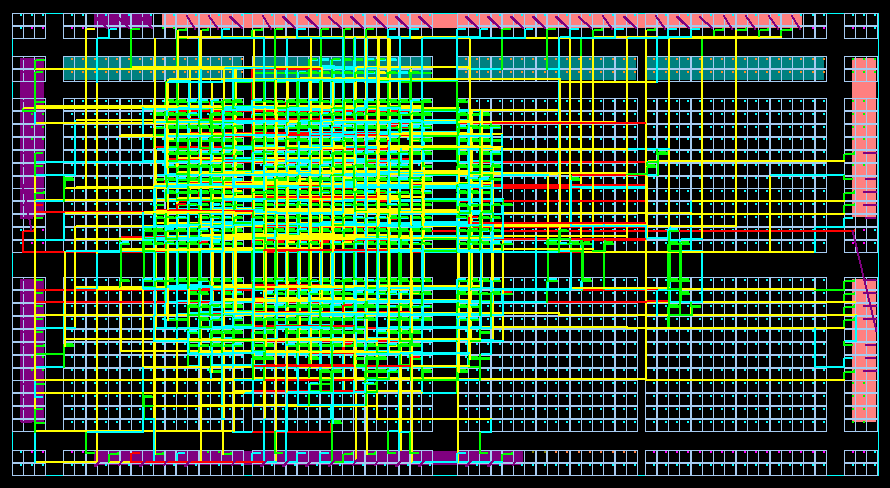

Can you believe that the source code synthesised and place/routed on first try and reached an estimated 49MHz performance on A3P060 ?

The core occupies about 570 versatiles (3-input cells) which leaves 2/3 of the FPGA (1K LUT3) for GPIO and peripherals :-) [I originally expected about 700]

The source code is not used correctly (many registers are mapped to I/O pads, an artefact from the coding style) so performance can only increase and the system fits nicely in the small #ProAsic3-Stamp !

There is still a lot of work to do but it's looking great so far.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.