Hardware design

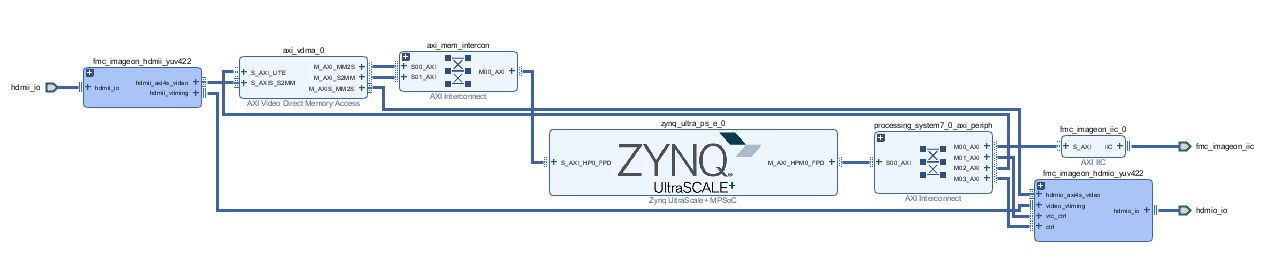

The demo is based on a customed design platform developed in Vivado 2017.2.

The resolution of the input and output video data is set at 1280x720 with a 65MHz frequency rate.

For the video input and video output we used respectively HDMI input IP and HDMI output IP that already existed. The HDMI input component (ADV7611) and the HDMI output component (ADV7511) are configured by software at start up.

A UART interface is used to communicate and configure different part of the system (HDMI, VDMA, VTC).

The Xilinx® LogiCORE™ IP AXI VDMA core provides the high-bandwidth direct memory access between the DDR4 memory and the HDMI peripherals.

This is a simplified view of the hardware design using Vivado 2017.2

Software design

Our demo is a bare-metal application executed on the ARM Cortex A53 processor. The project was developed with SDSoC2017.2 from Xilinx.

In our software the edge detection code is accelerated in hardware to improve performances.

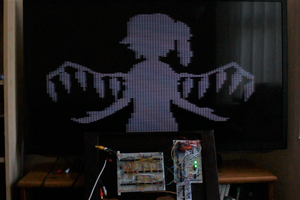

The edge detection algorithm is producing a black and white video stream. Edges in each frame are marked as white and the remaining part of the figure is set as black.

The edges are detected by a Sobel filter. Each pixel is filtered by a 3x3 2D FIR filter. A nonlinear decision on the output of the filter provides information as to if the pixel is part of an edge or not. All computation is performed in fixed point. The Sobel filter is applied on the left half of each video frame for display purposes.

When the filter is accelerated, the main purpose of the software code is to control the advancement of VDMA frame pointers. Indeed, a triple buffer is used in order to display the newly computed frame a soon as the Sobel filtering is finished while, at the same time, processing the following input frame.

The output display is vertically split in half. The right side displays the video before being processed while the left side displays the video processed with a Sobel filter.

The software has been developed to highlight the benefit of hardware acceleration. In that respect, the output video display switches between the data processing done in software then done in hardware. The changes occur about every 15 seconds and highlights the greater performances achieved once the software is accelerated. In our case, the FPS is closed to 40 times faster:

· 0.73 fps (software)

· 31 fps (hardware accelerated)

Demo

This video demonstrates the use of the Lynsyn board to monitor the power usage when running the EMC2 HDMI in to HDMI out application with hardware accelerated Sobel filter.

Sundance Multiprocessor

Sundance Multiprocessor

Santiago Germino

Santiago Germino

Hi, Can anyone share the application project (Vitis Project). I made but I am facing one error #include "sds_lib.h" is not there because of the build is failing.