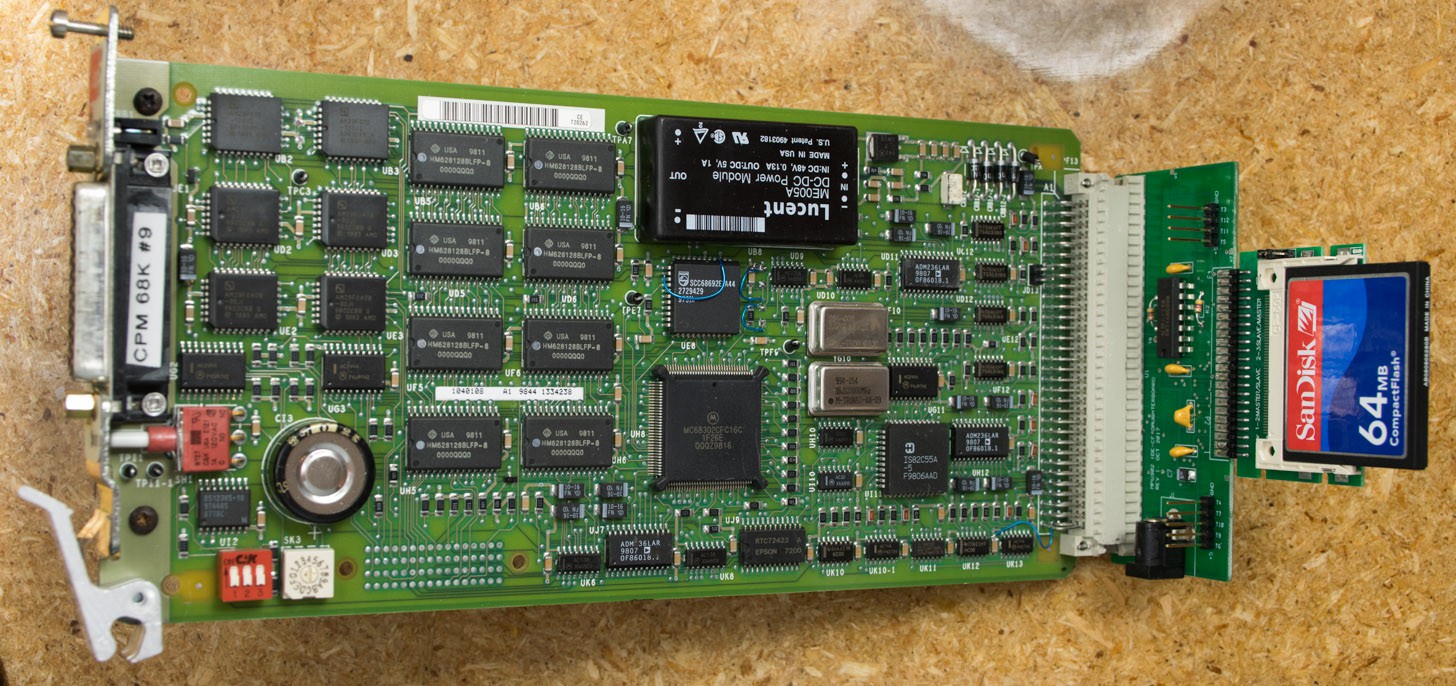

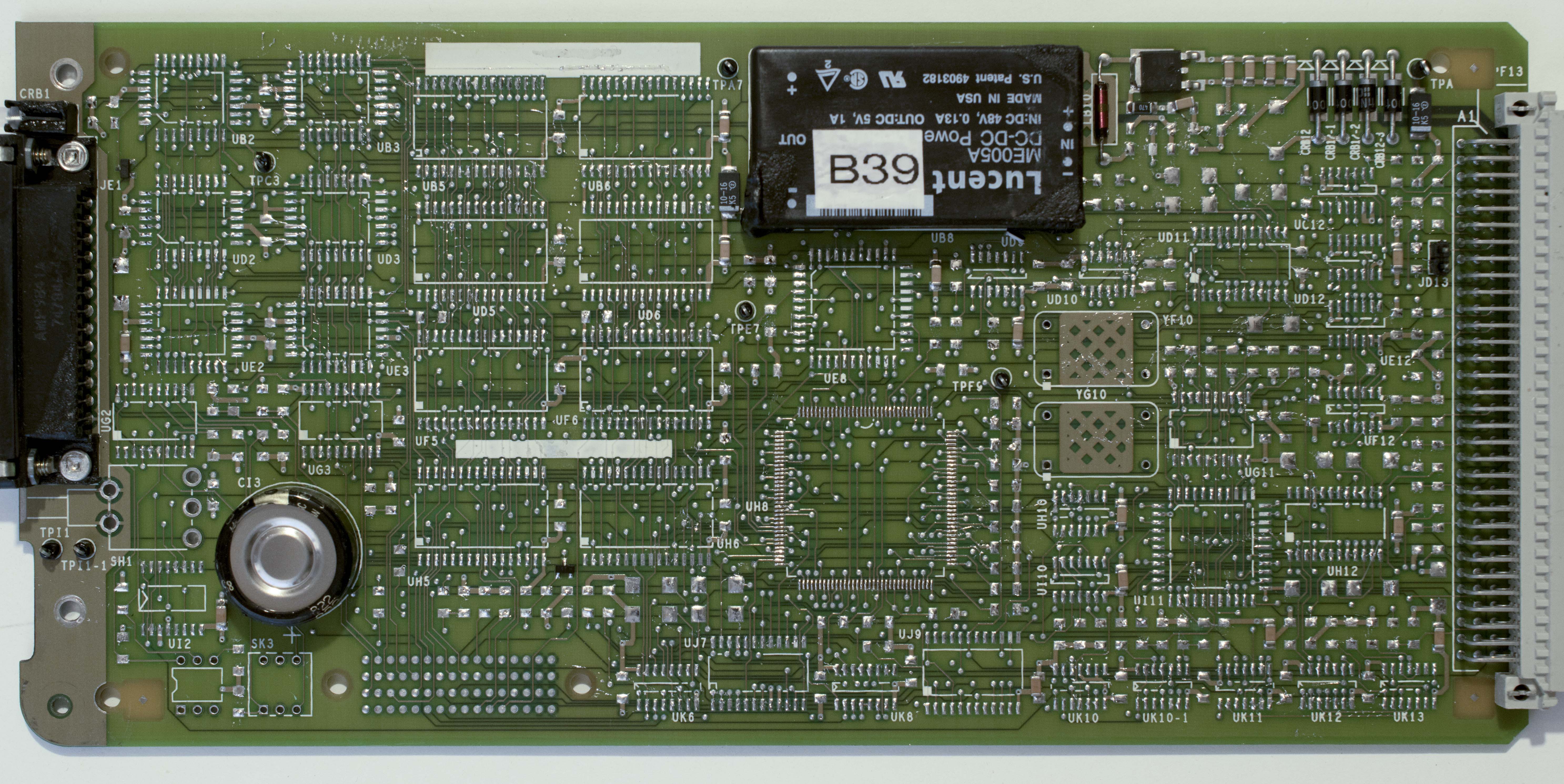

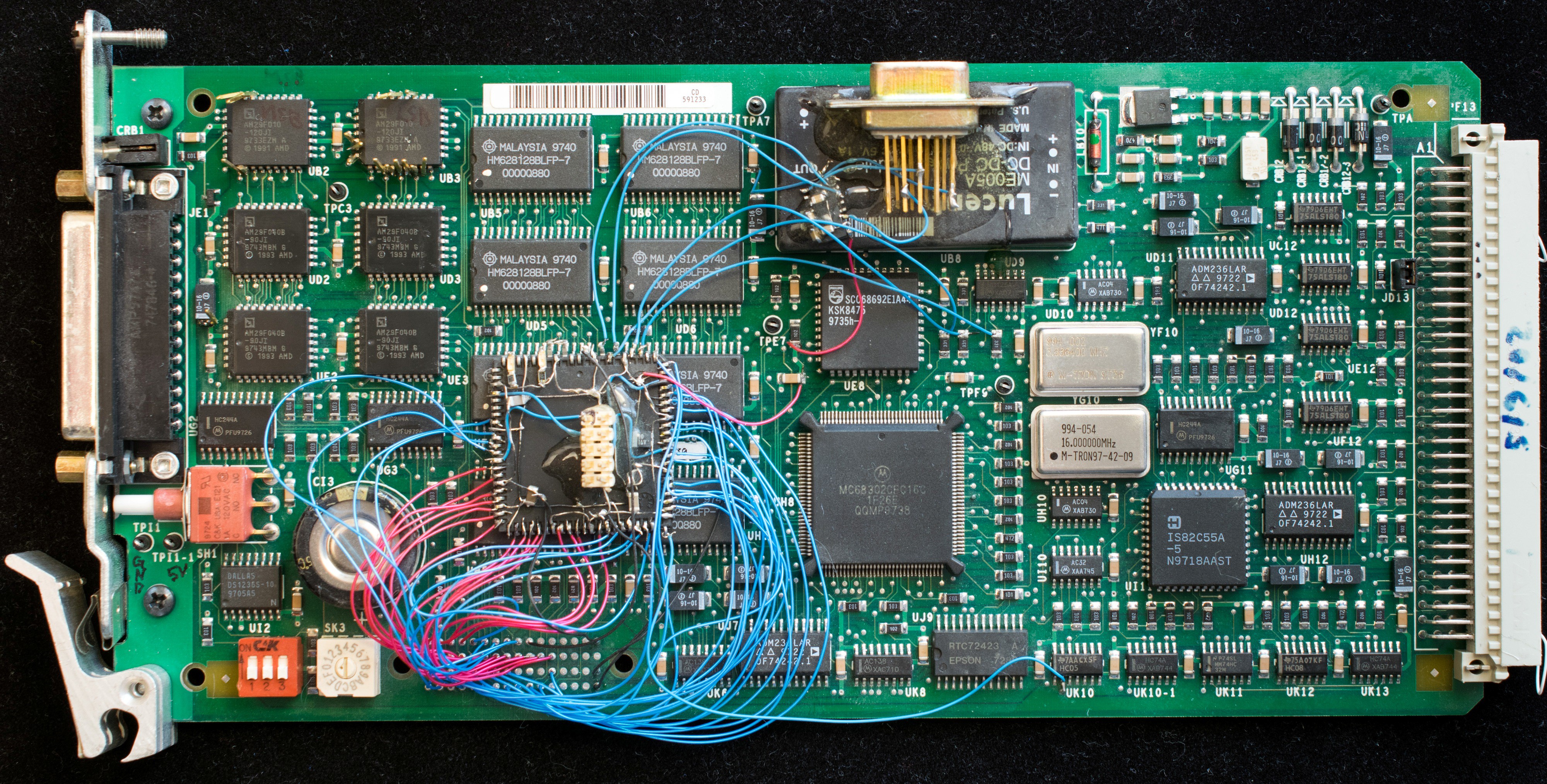

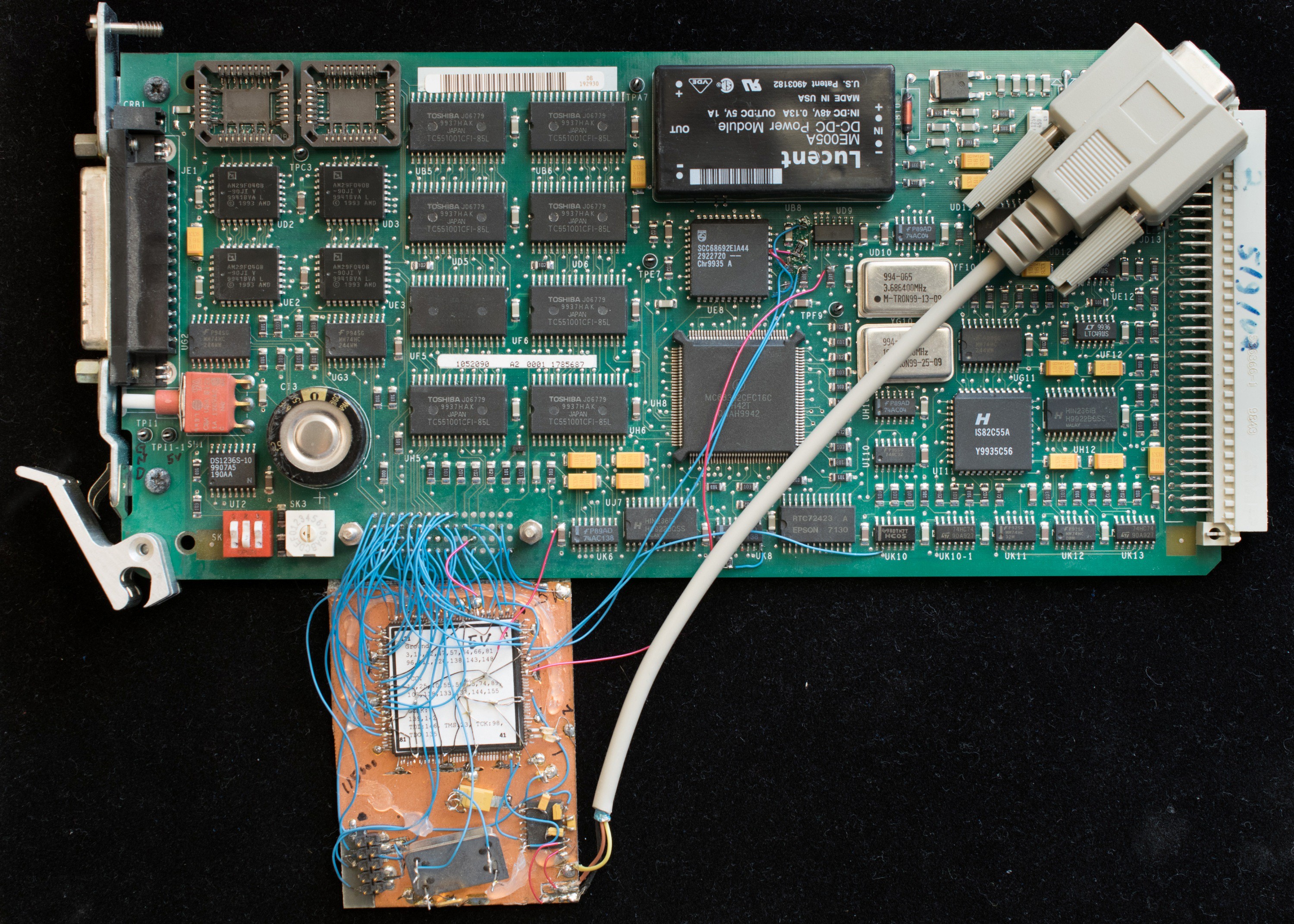

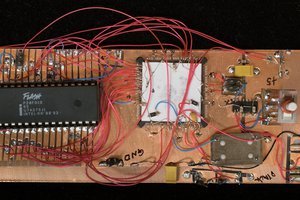

SPX MPU is a general-purpose SBC with the following features:

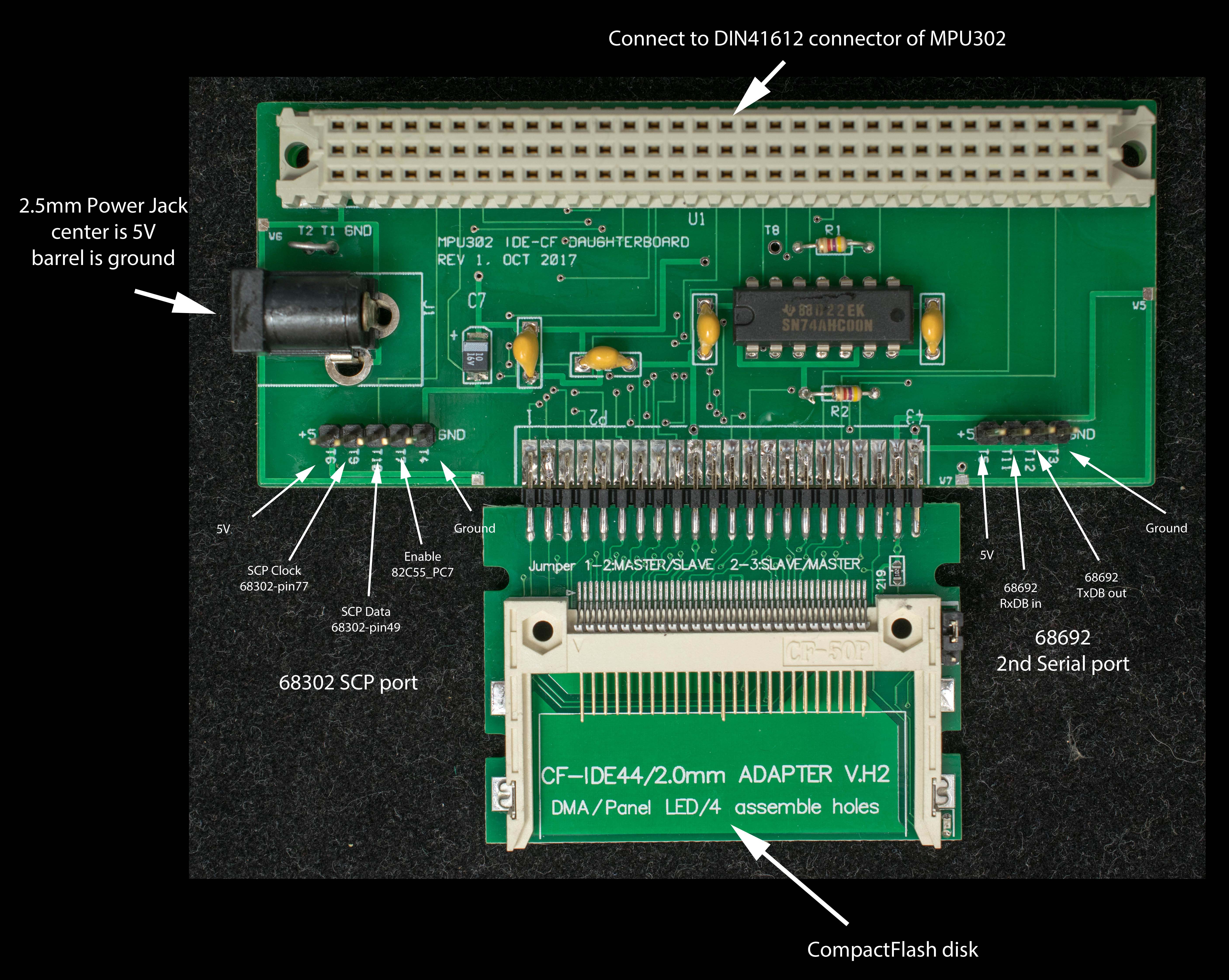

MC68302@16MHz with SPI and 3 SCC,

256K bytes boot flash,

2 Megabytes application flash,

768KB static RAM plus 256KB RAM backed by super capacitor for a total of 1 Megabyte RAM,

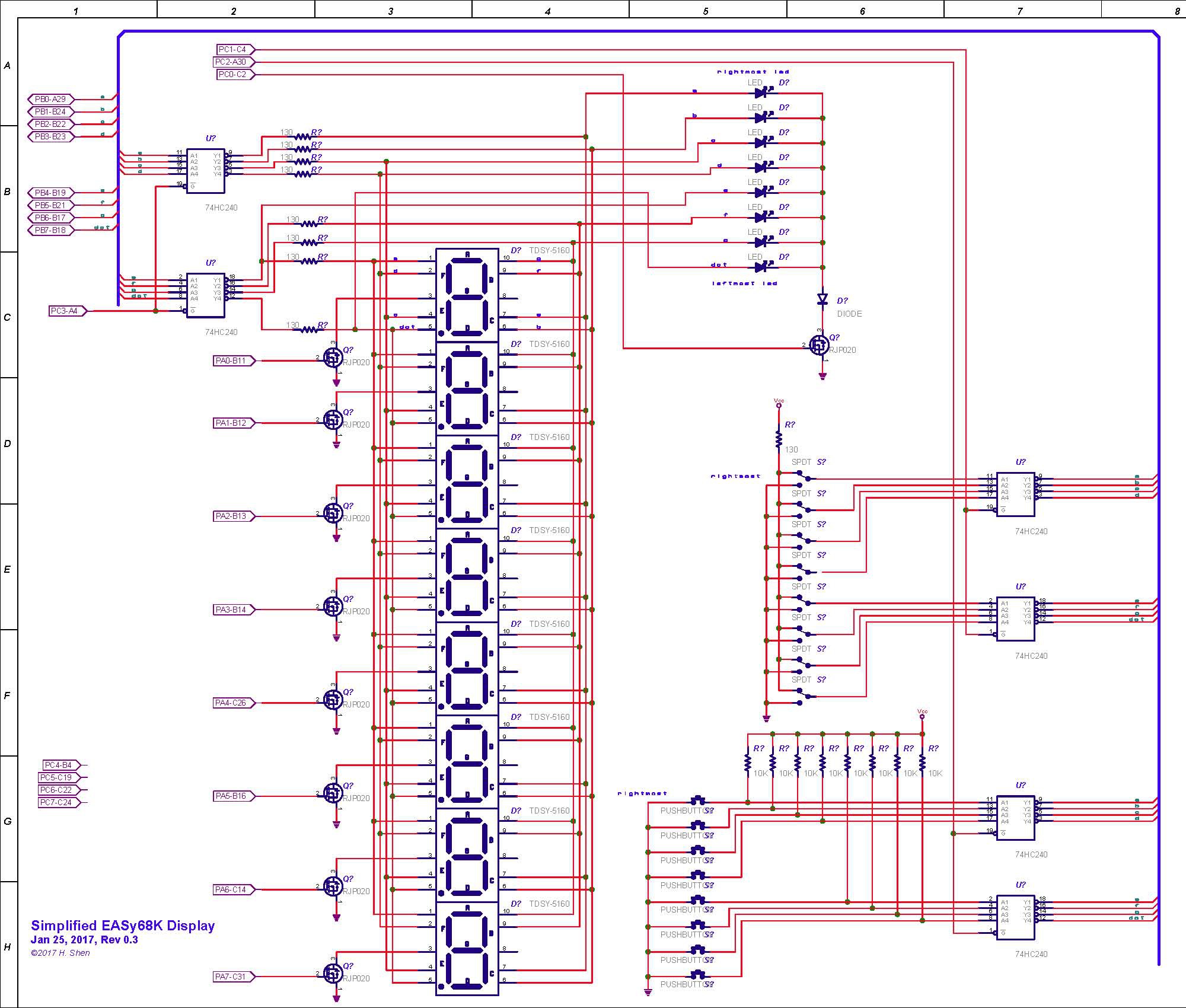

82C55 programmable peripheral interface,

68692 Dual UART,

Real time clock,

16 discrete inputs,

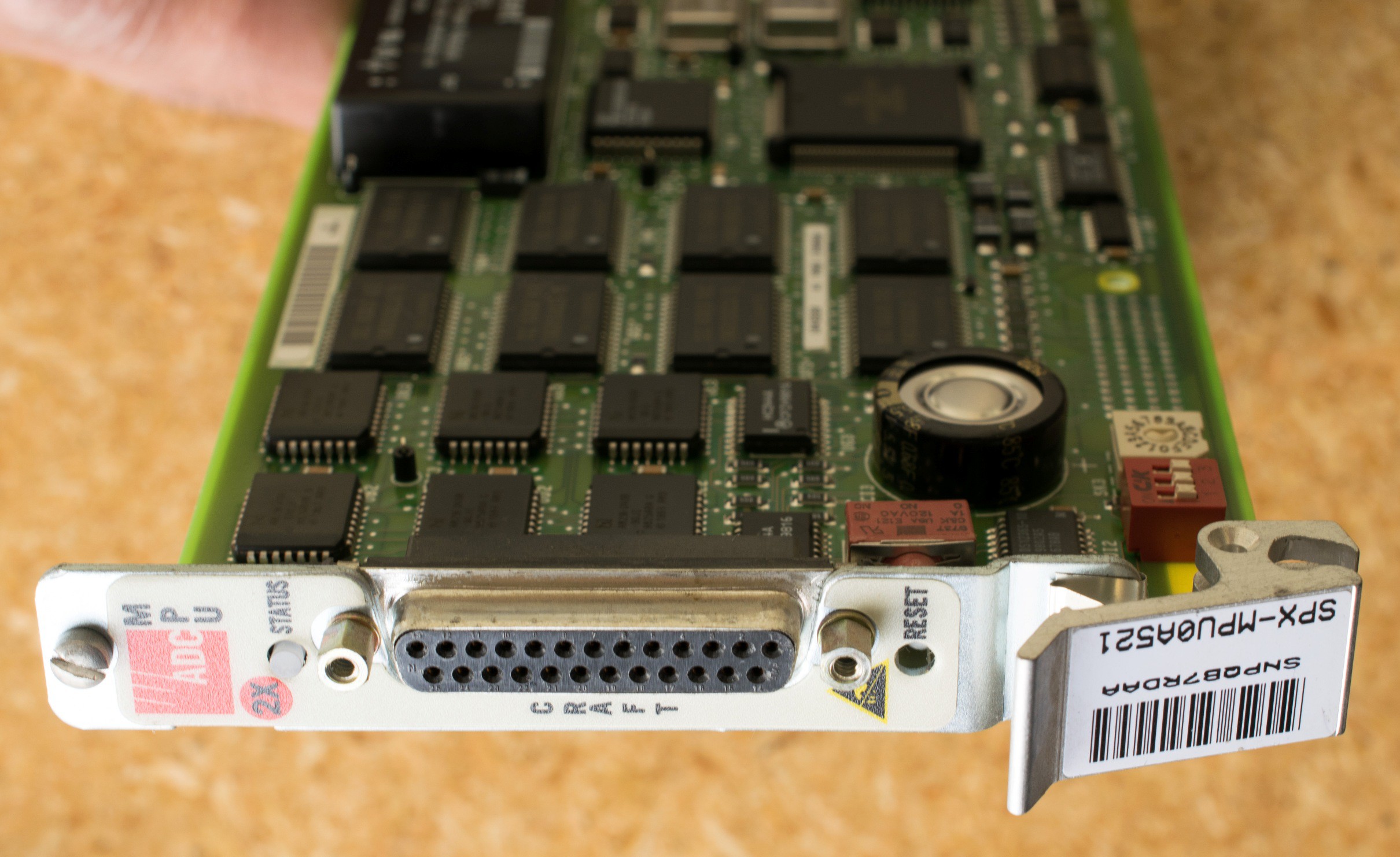

Connect to backplane via 96-pin DIN41612 connector,

48V to 5V DC/DC converter ,

Power consumption at 5V is 250mA nominal.

Chronological list of projects

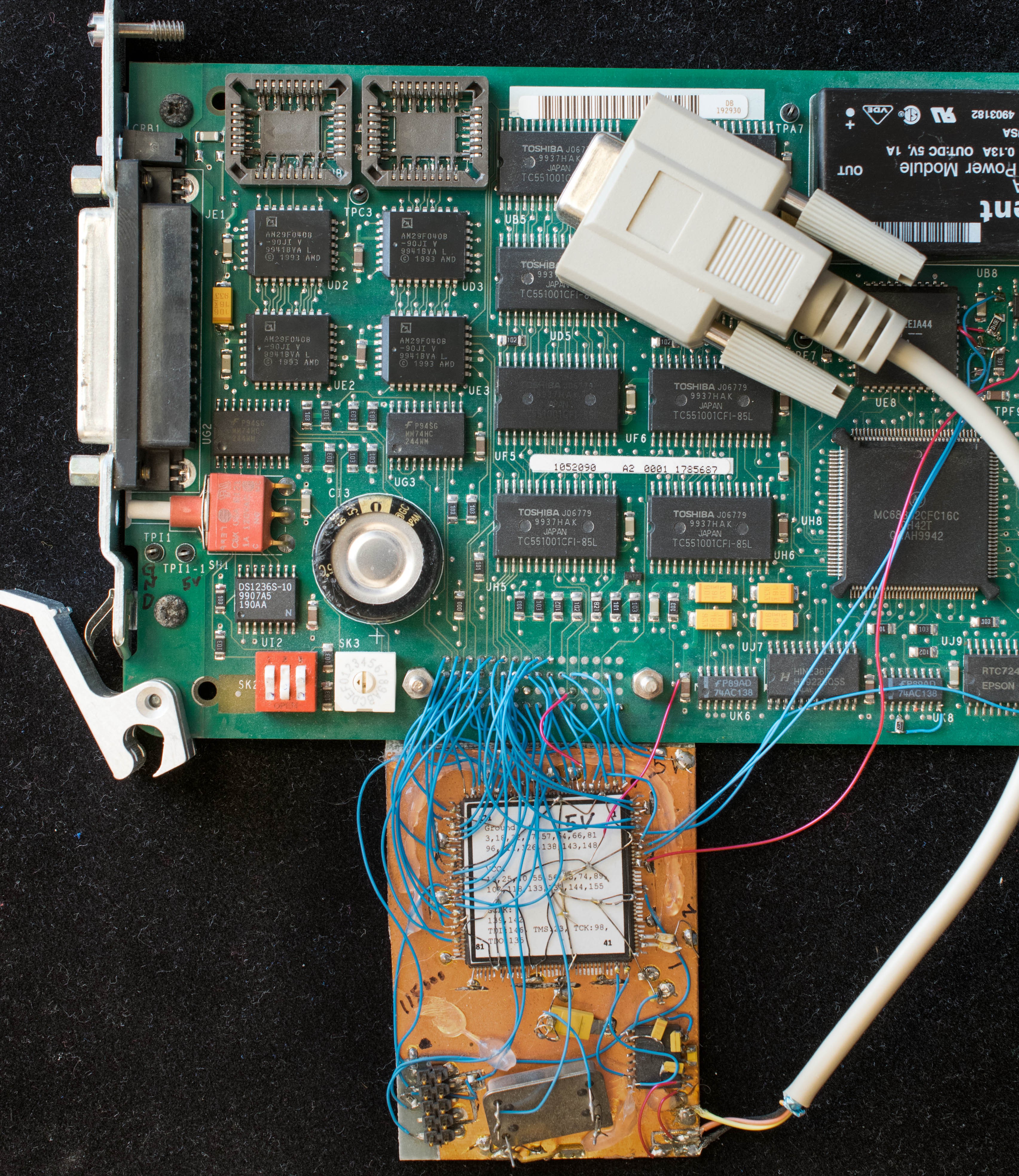

Flashback, exploring the salvaged SPX MPU board

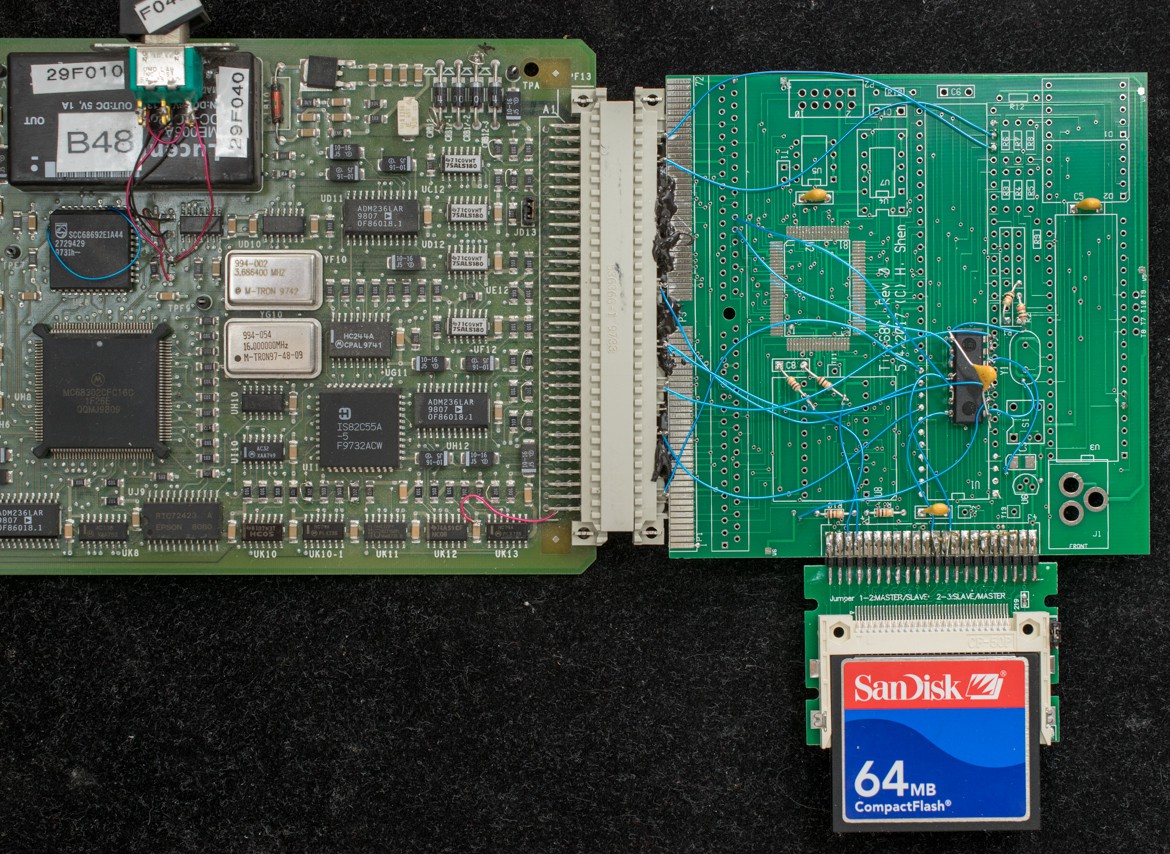

Paradigm Shift, A different way to reverse engineering the SPX MPU board

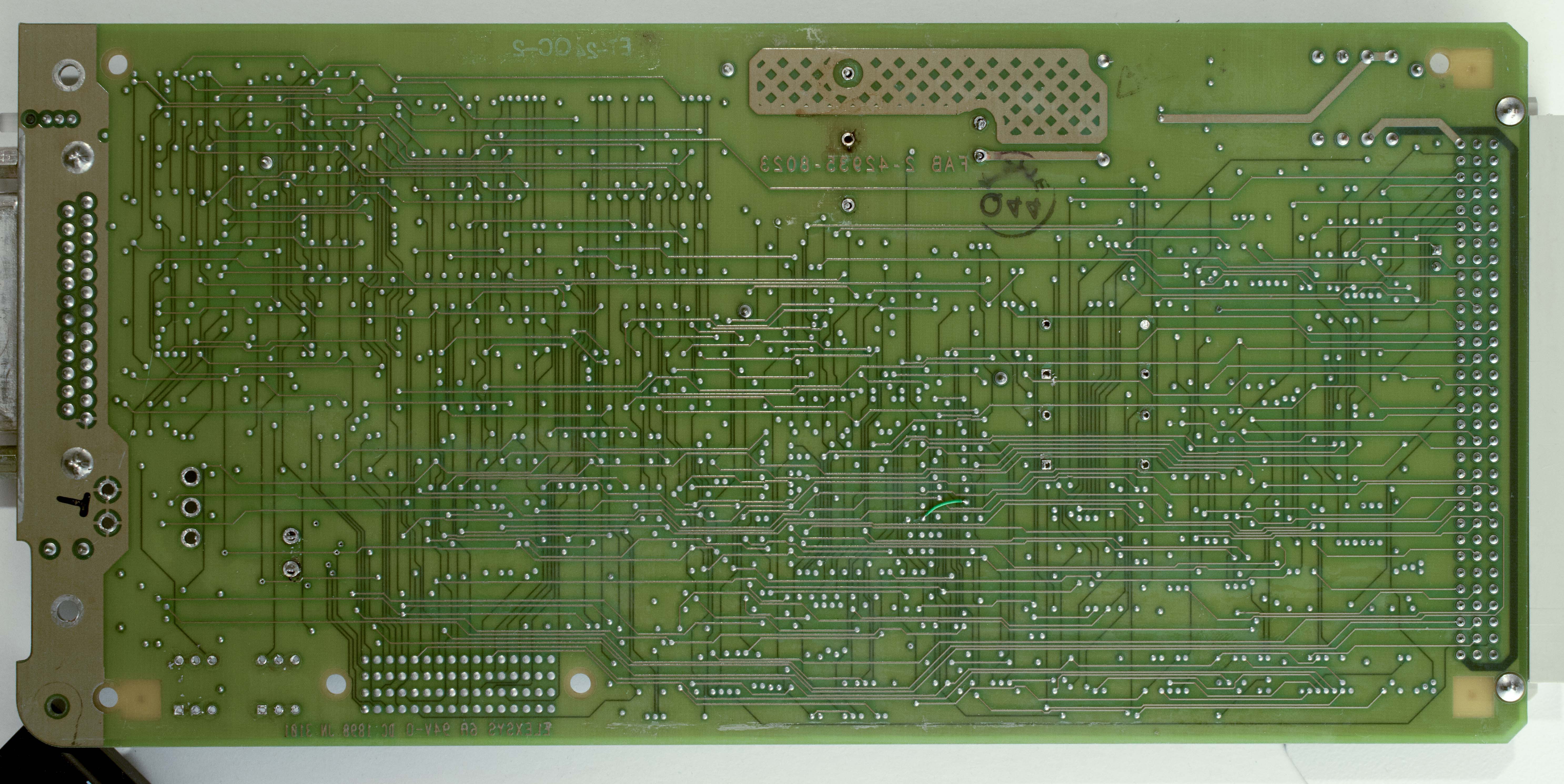

From PC board to Schematic, technique to extract netlist from pc board

Hijacked, taking control over the original software

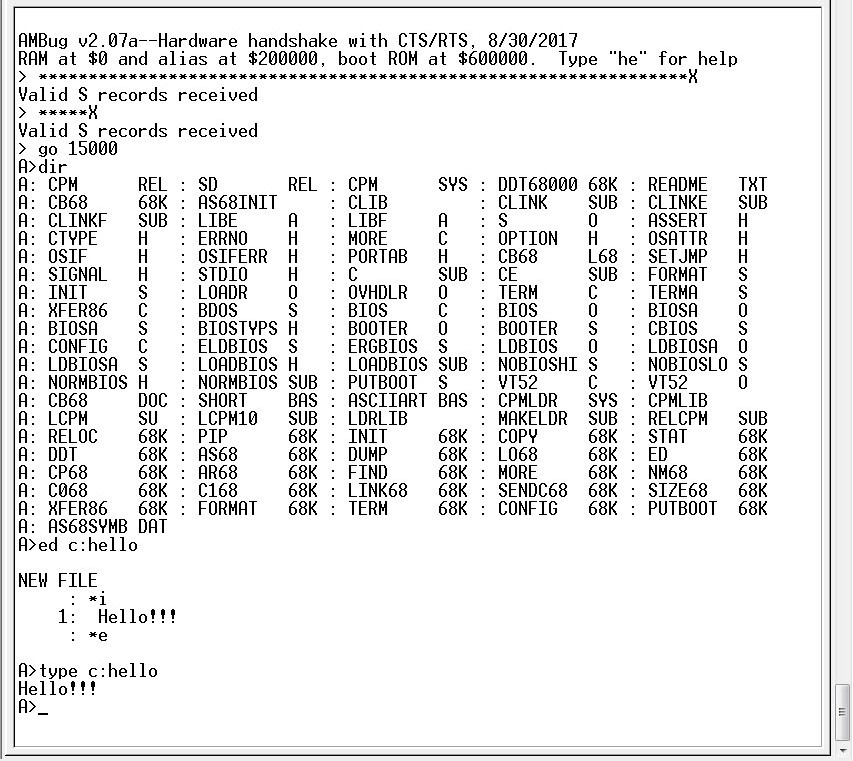

A Working Monitor/Debugger, installing my own monitor/debugger

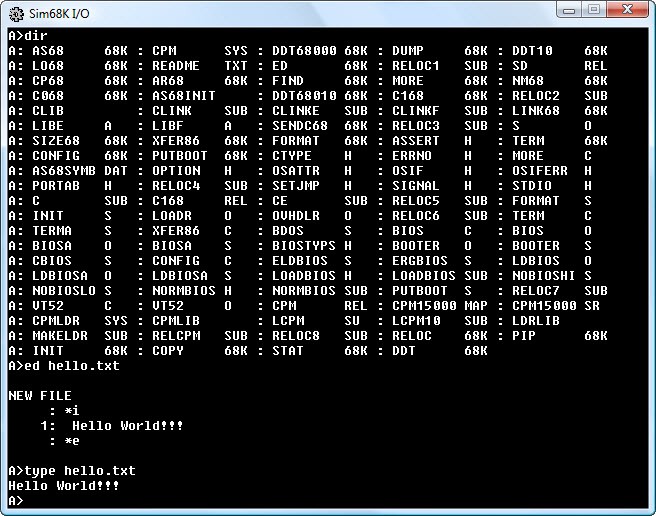

porting CP/M-68K part 1, 4-part projects on porting CP/M68K to MPU302

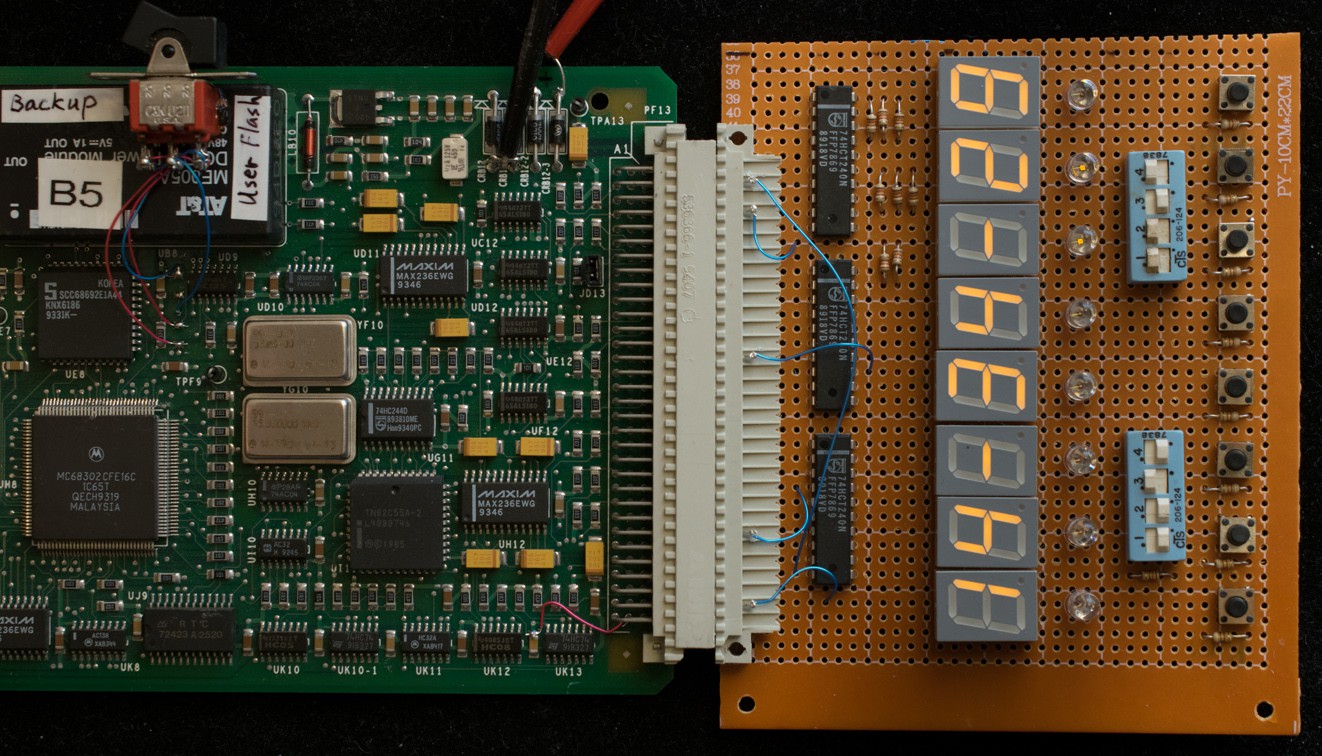

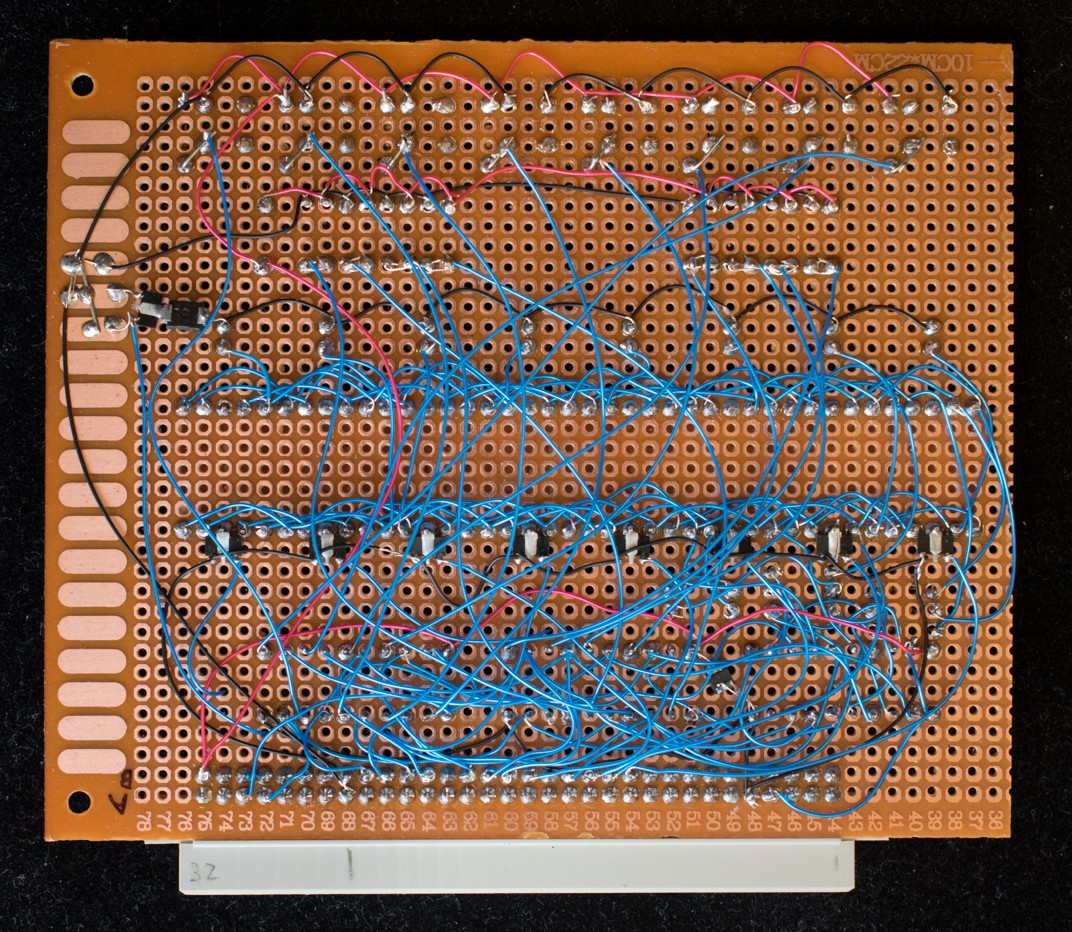

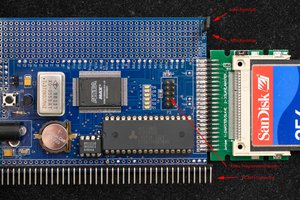

Let There Be Light, a project with MPU302, adding 7-segment display to expansion port

Plasmode

Plasmode

J.B. Langston

J.B. Langston

Hi,

Are you looking for a SonePlex SPX-MPU board? I just list it on eBay, but it is the original unmodified board. Let me know if you are interested in board modified for CP/M68K.

You also mentioned 68030 SBC. I've designed one and it is in development stage. I don't have one ready for sale.