TRIADOR specification was born in summer 2017 during long discussion on my forum http://nedopc.org/forum/ when Dmitry asked forum users to think about simple, but powerful enough ternary hardware design that could be built from TRIMUXes (dual ternary multiplexers that I accidentally "invented" in 2010 when tested limits of DG403 switching chips). Then he finally built it in reality :)

I don't have so many TRIMUXes (yet) so I decided to create my own version of TRIADOR (slightly different from Dmitry's creation, but still reflecting the same specification) in Logisim (digital electronics simulator written in Java). I already had most building blocks from 2011 when I simulated ternary counter for ternary clock:

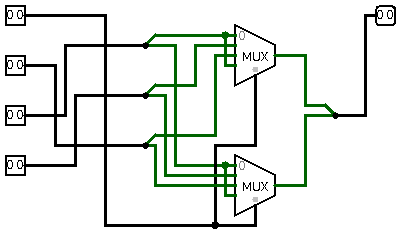

Main idea was to represent every ternary signal as a bus that consists of 2 digital wires - 00 will be 0 (O), 01 will be +1 (P), 10 will be -1 (N) and 11 will be forbidden combination. So in 2011 I created 2 most generic ternary blocks (using Logisim "binary" components) - ternary MUX (single ternary multiplexer):

and ternary MEM (single memory cell with 1 control input and 2 data inputs):

Everything else was built out of these two (in reality MEM could also be build from MUXes with loops as Dmitry showed here, but not in Logisim). Below you can see Logisim model to simulate TRIADOR without extension instructions and this model already is big enough to make Logisim crash most of the times when it's loaded:

https://cdn.hackaday.io/files/285791222723936/ternary_circ.zip

Source code for this could be found on GitLab: https://gitlab.com/ternary/ternary

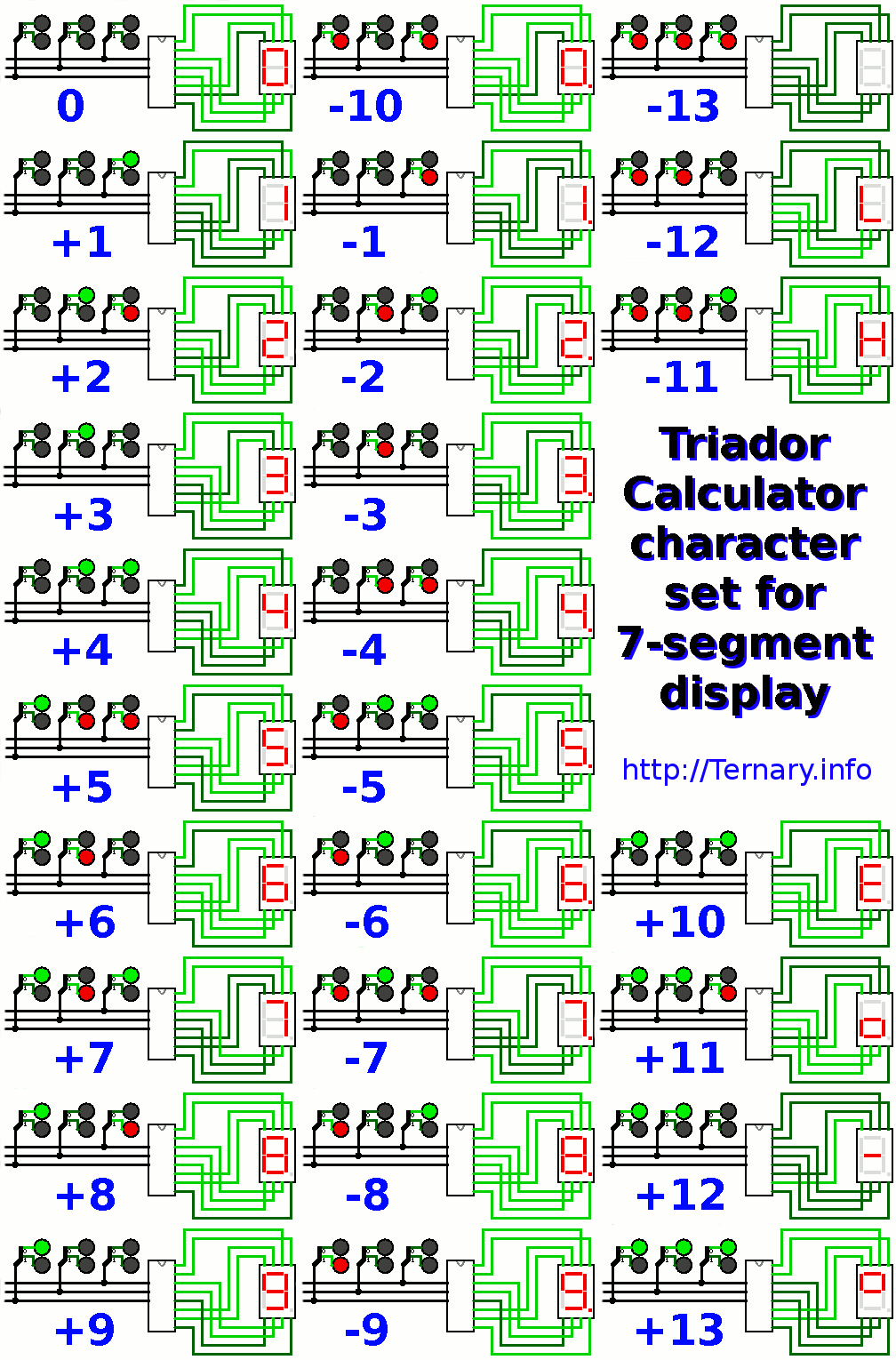

Here you can see additional indication - 6x6 Red/Green LED matrix and eight 7-segment indicators connected to outputs of TRIADOR registers. This is how I represent triads on 7-segments:

This is a way to build a calculator (eventually). But because of unstable behavior of the model I stopped in November 2017 - now I want to go further with conversion of this model to netlist that could be translated into (1) C program for further compilation and testing and (2) VHDL program for flashing into some FPGA board to create more or less affordable real life application of ternary computing ;)

P.S. and may be even (3) CMOS full custom IC as part of my Shared Silicon project :)

SHAOS

SHAOS

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.