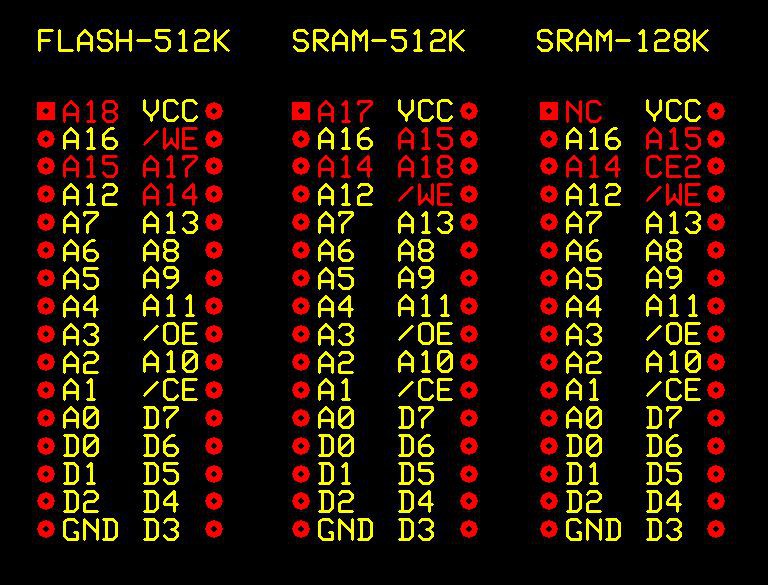

There are some slight differences in the layouts of 32 Pin DIP SRAM and FLASH.

Most of the differences are not a problem. For SRAM it doesn't matter if you mix up the Address or Data pins as long as Address and Data pins are grouped separately. ie It doesn't where the data goes as long as it comes back from the same place. So I ignored most of that and just assumed the Address pinout of the FLASH because that does matter.

Apart from that there is the issue of /WE and one address pin being swapped comaring SRAM and FLASH. I could have just swapped these pins on the SRAM board but I left it as an exercise in VHDL to fix it with code.

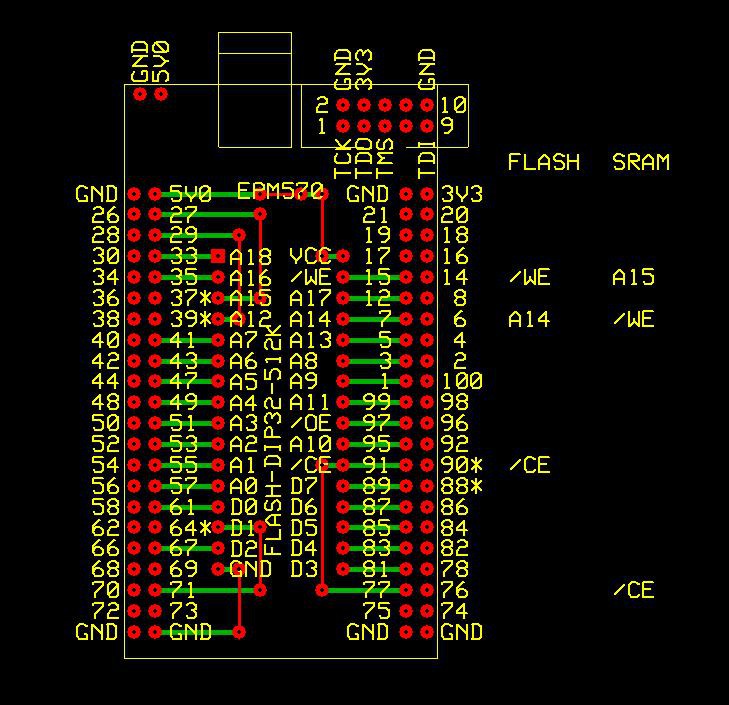

I decide to connect all the pins except /CE in parallel to save pins on the CPLD.

The SRAM is 512KBytes 25nS and the FLASH is 70nS.

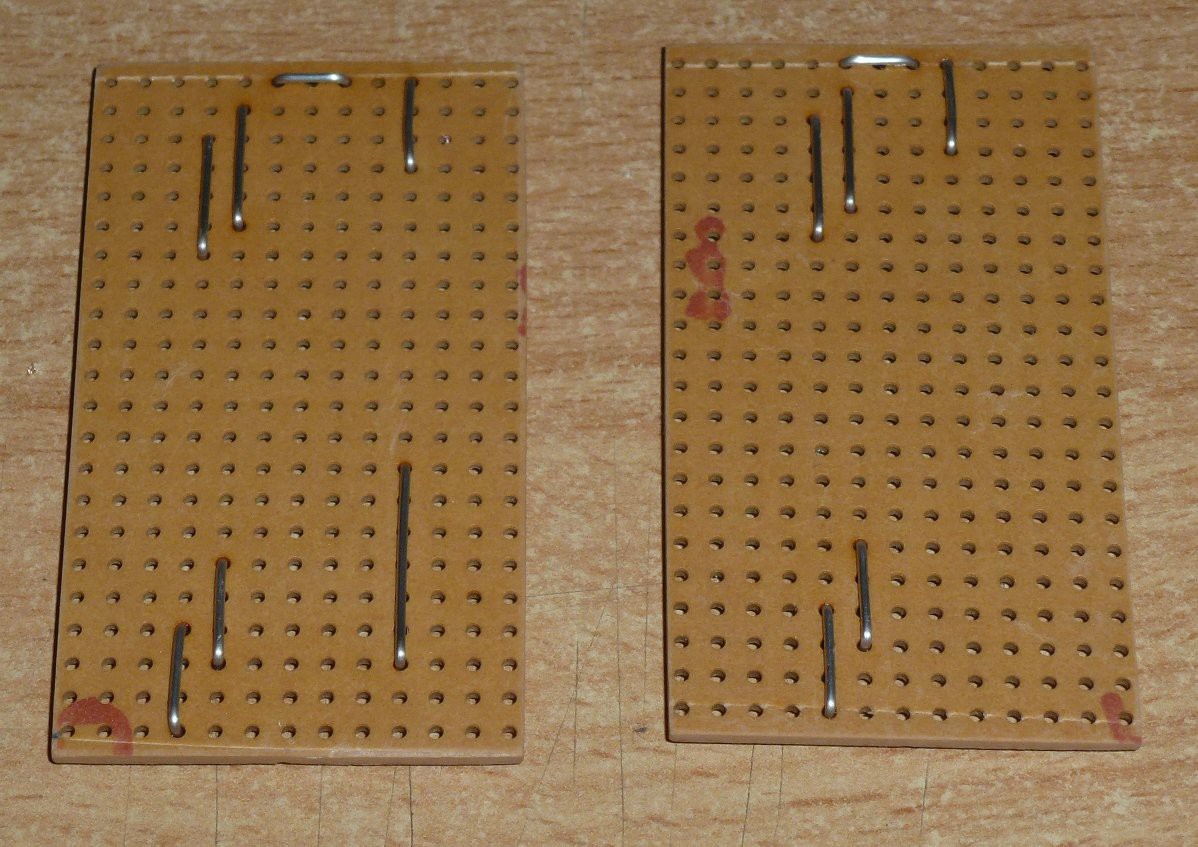

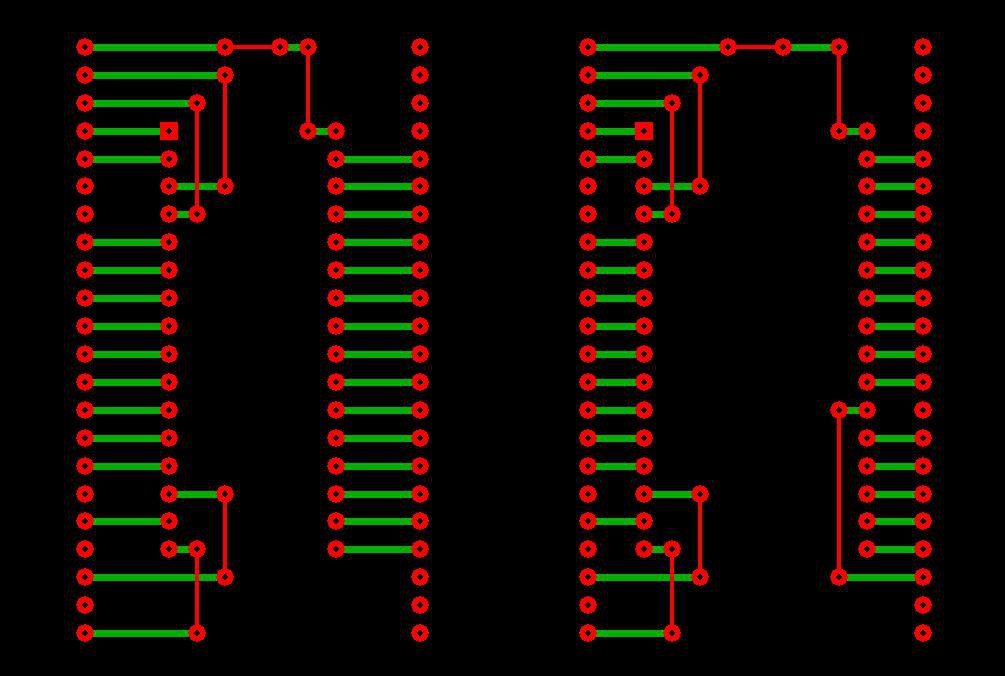

Here are the equivalent PCB layouts (FLASH on left, SRAM on right) -

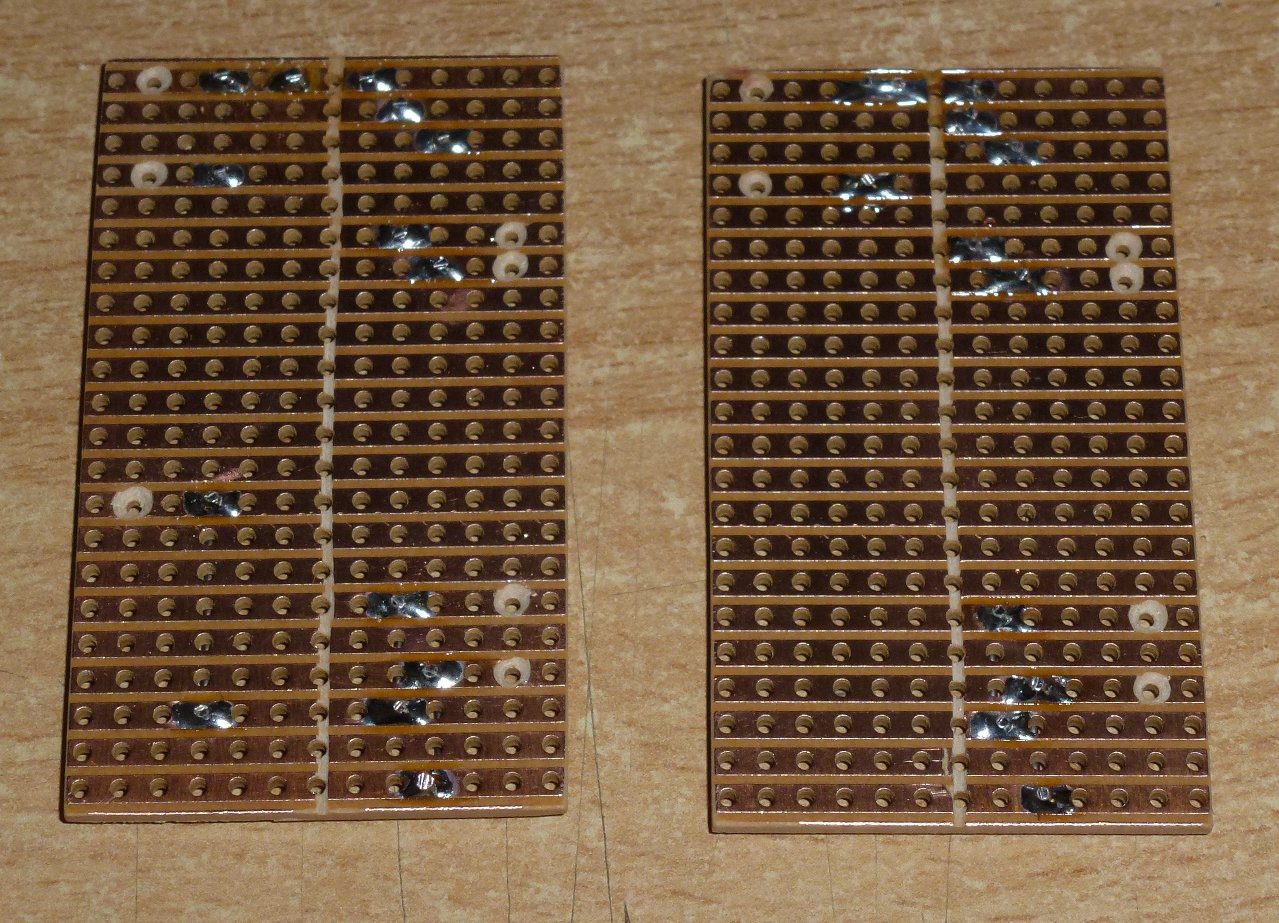

And dreaded Vero layout (SRAM on left, FLASH on right) -

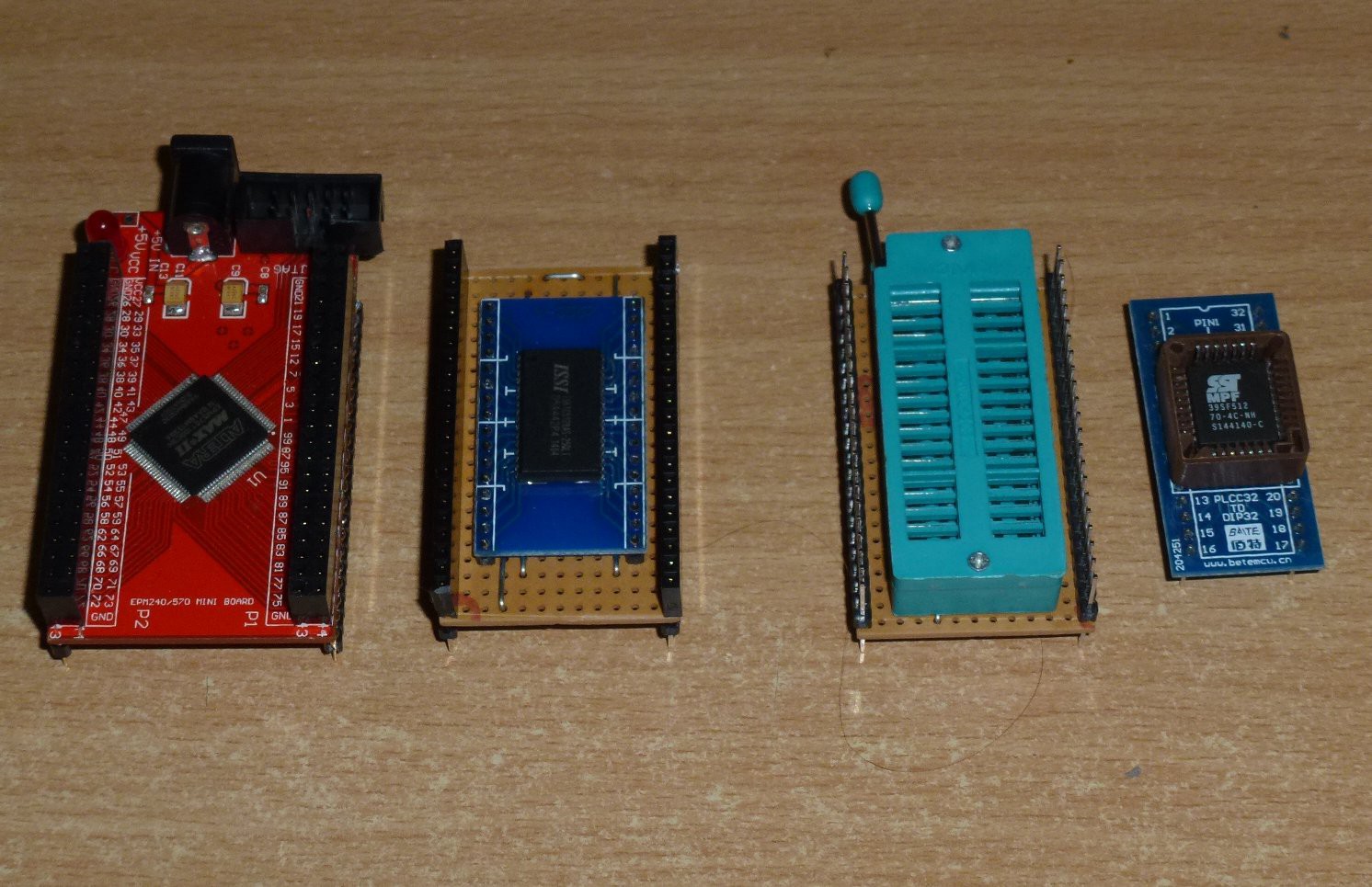

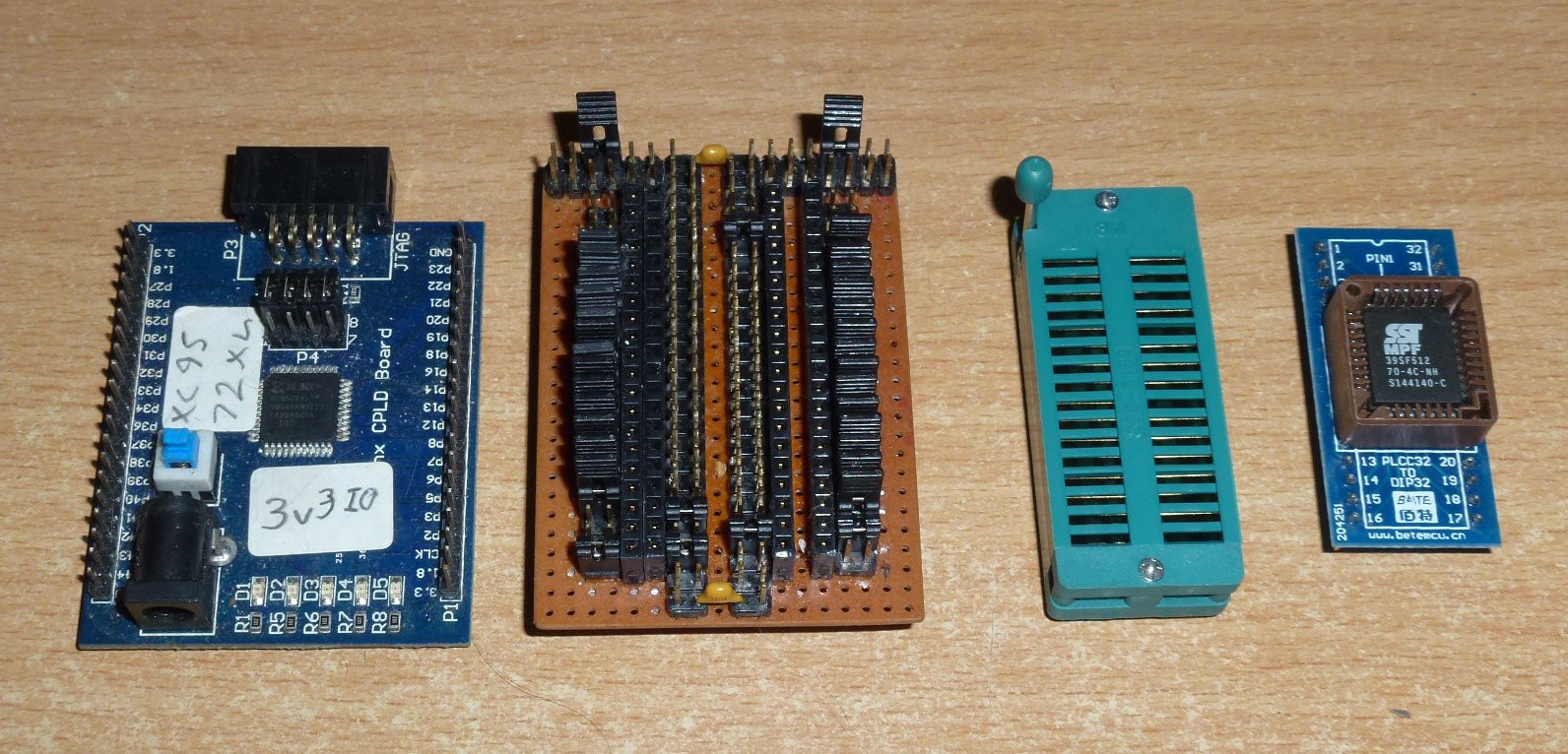

They all connect together this way -

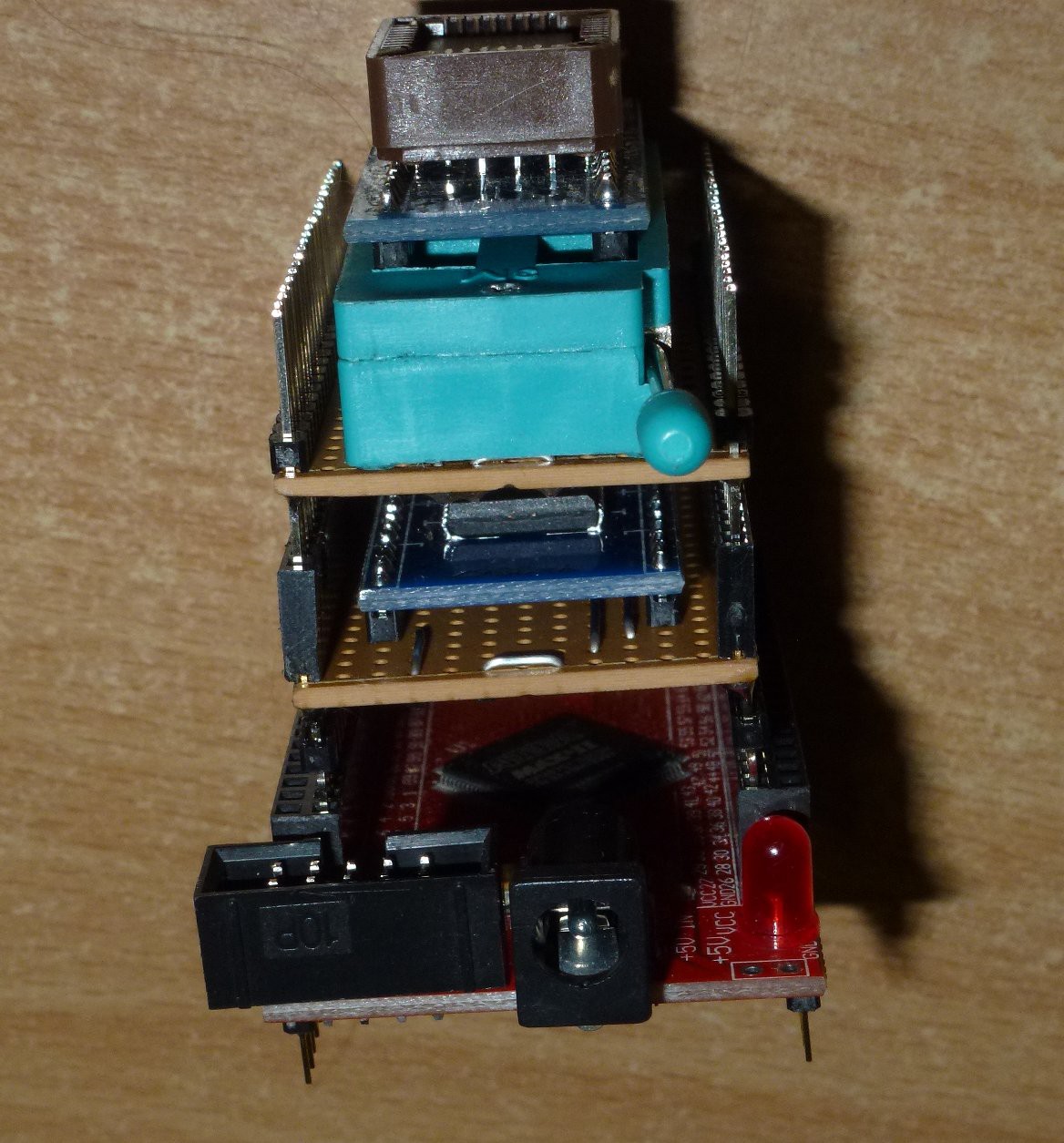

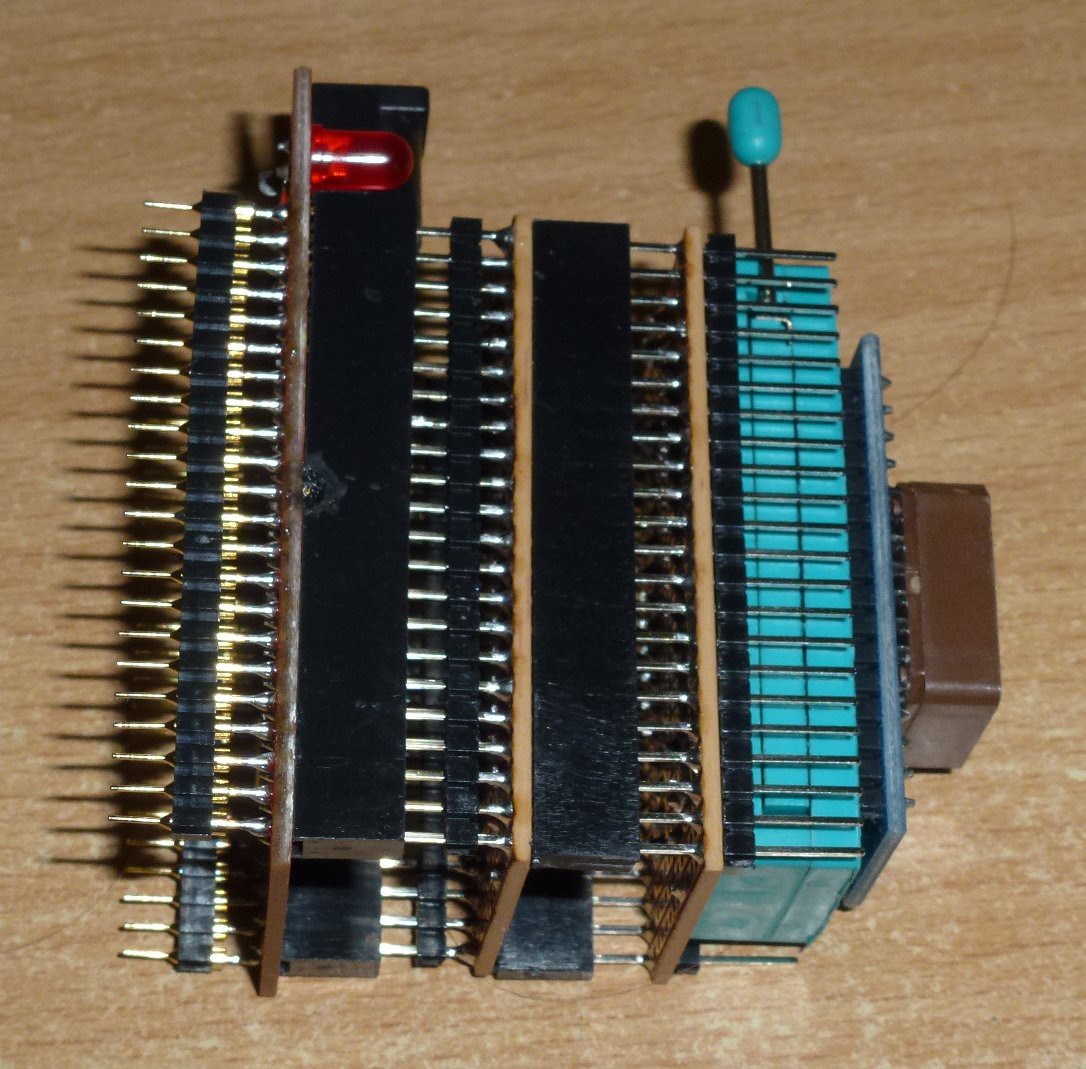

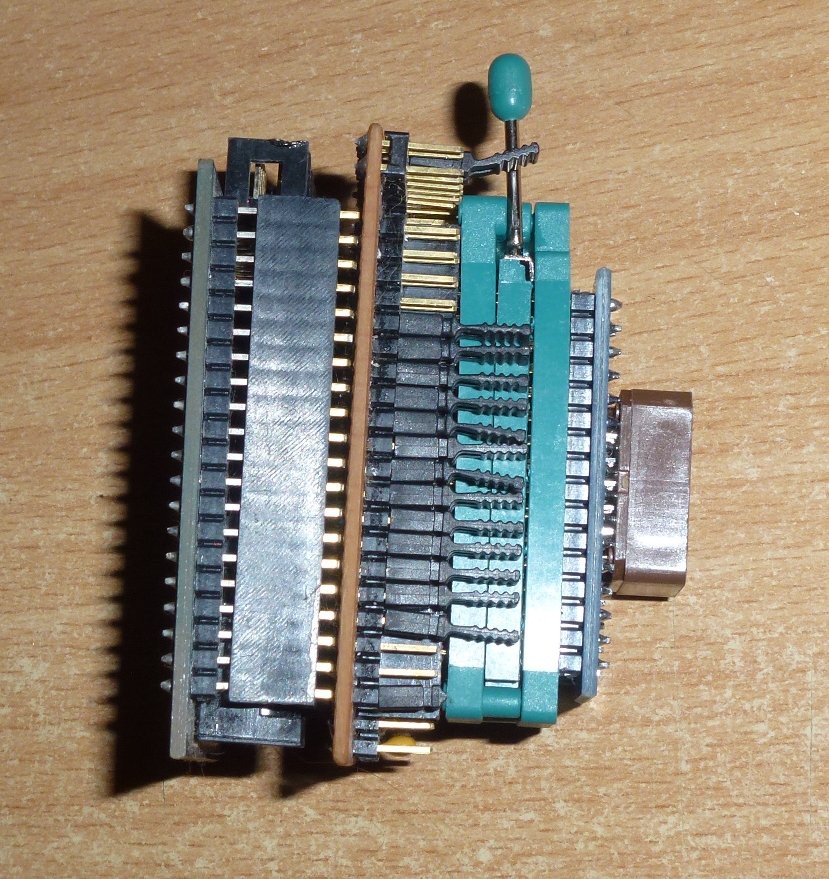

Assembling the bits -

To program the FLASH I will be using a stack made in a similar way. It connects to an Arduino.

The programmer was made for a 64KB FLASH so I have to go and rewrite the Arduino code and VHDL (It's a Xilinx chip) so that it can program larger FLASH - up to 512KB.

Then I have to write the VHDL for the Altera development board - I haven't even started this yet.

Next steps are - Write VHDL for VGA output. Dual port the FLASH and SRAM with the CPU bus having priority (like it was in the TRS80). Add the CPU and see the 'READY>' prompt (milestone 1 - Level Up).

Then convert to time division bus multiplexing. After that I can start to worry about I/O such as keyboard and the dreaded pin count. Will it fit in a 100 Pin CPLD???

OK, I am off to do what I enjoy more and play with some code.

Hacker404

Hacker404

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

I dig the stacking idea, functional and it looks cool too.

I have a few ancient DIP CPUs that actually have sockets for the EEPROM built-in, on top... stacking's awesome :)

Are you sure? yes | no

lol thanks.

Are you sure? yes | no