DIPSY

You might have hit that point when your microcontroller peripheral just doesn't have exactly the features you need:

Dipsy comes to the rescue!

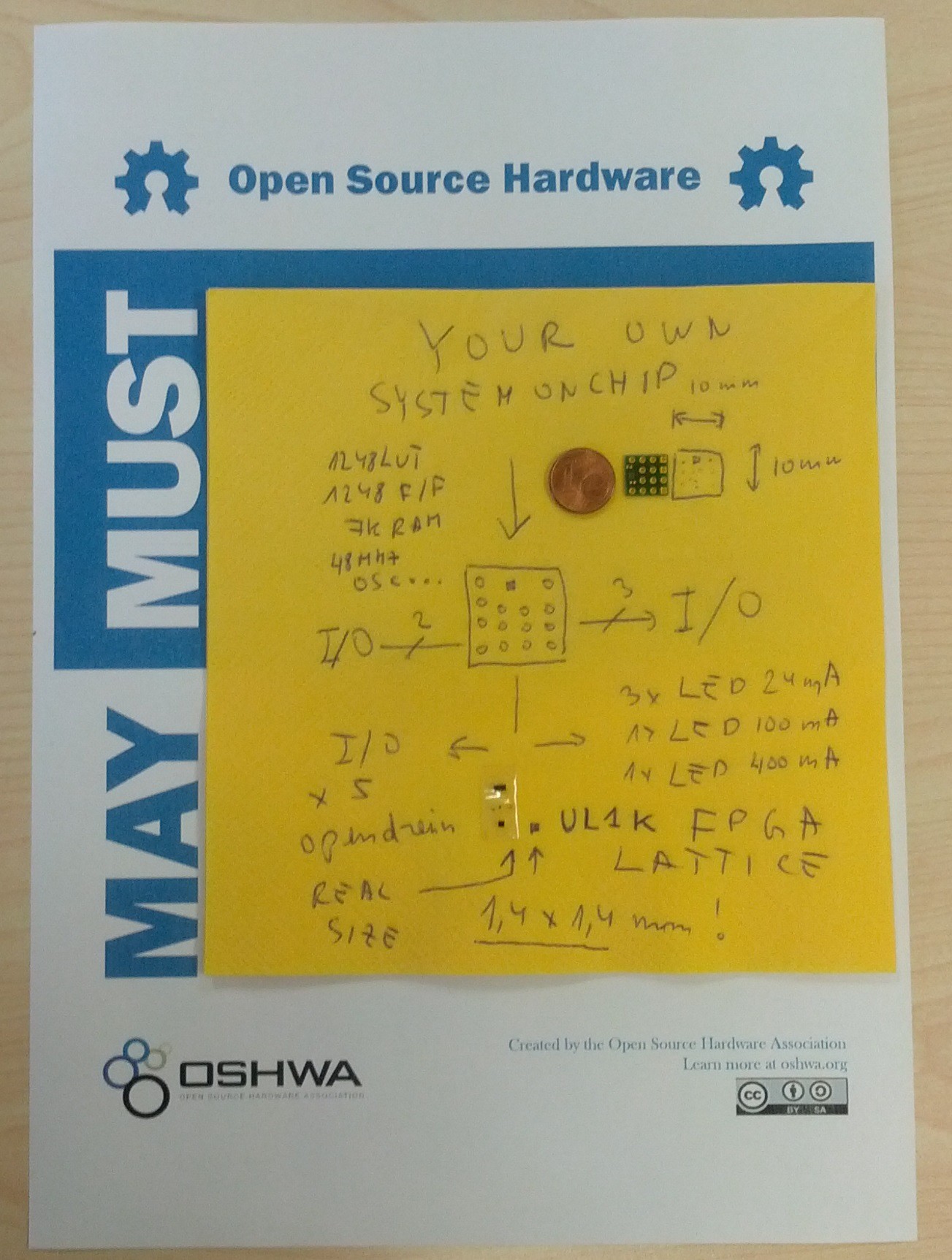

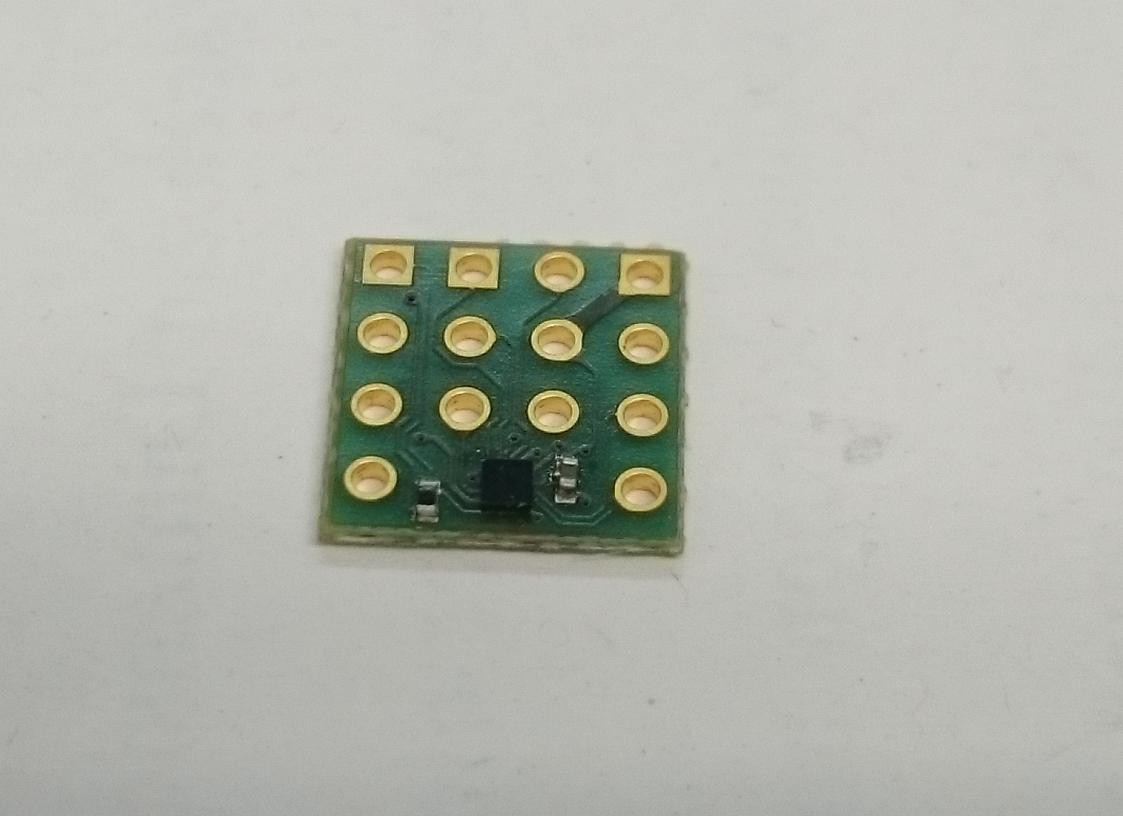

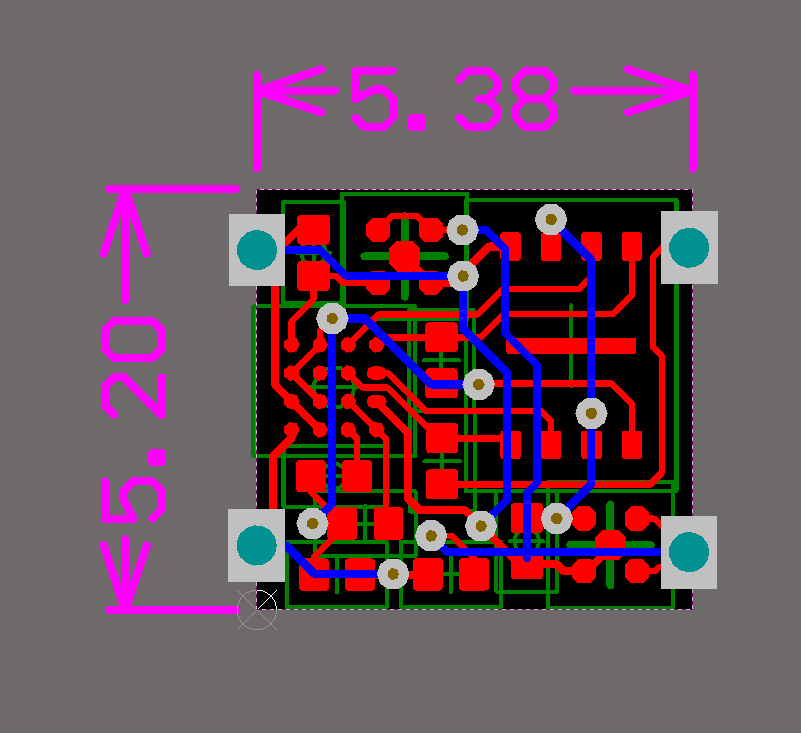

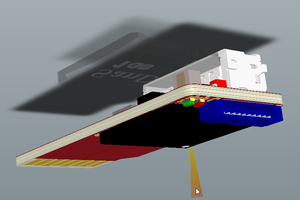

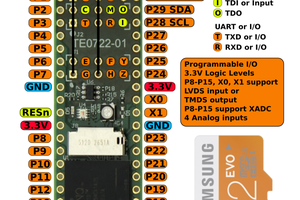

It's a tiny FPGA (Lattice iCE40UL1K-SWG16) on a tiny 10 x 10 mm², breadboard-friendly PCB:

With 1284 logic cells, 7 kB RAM and a few extra goodies in this tiny package, it's the perfect addition to your already breadboarded prototype, and it can also be integrated into a pcb using simple pin headers.

Learn FPGA basics with dipsy!

Learn Verilog or VHDL with dipsy. Large FPGAs can be quite daunting, like this thing:

(picture: Keld Gydum, http://www.gydum.com/, picasa link)

and usually come in huge packages you don't really want. Dipsy is more like:

You'll quickly know your way around and the probability of meeting someone you don't even know is significantly lower.

What do I get with dipsy?

Apart from 1284 logic cells and 7 kB RAM you'll get

- Two built-in I2C interfaces

- a 48 MHz oscillator

- a 10 kHz oscillator

- IR TX/RX

- 3x 24 mA, 1x 100 mA, 1x 400 mA LED driver

- up to 10 I/O

- on-board core voltage regulator

What can it do for me?

It's the perfect addition to your project when you don't want that huge FPGA, probably in a QFP144 package, with a million logic tiles when everything you need is a custom device with a few PWM channels or something similarly simple:

- Like a servo controller.

- Or a WS2812 frame buffer.

- Or a device that maps your monochrome pixel data to something your color display can understand

- Or a fast data aquisition device with a small buffer

- Or a simple AVR core (yes, that does fit indeed!)

How do I develop software for it?

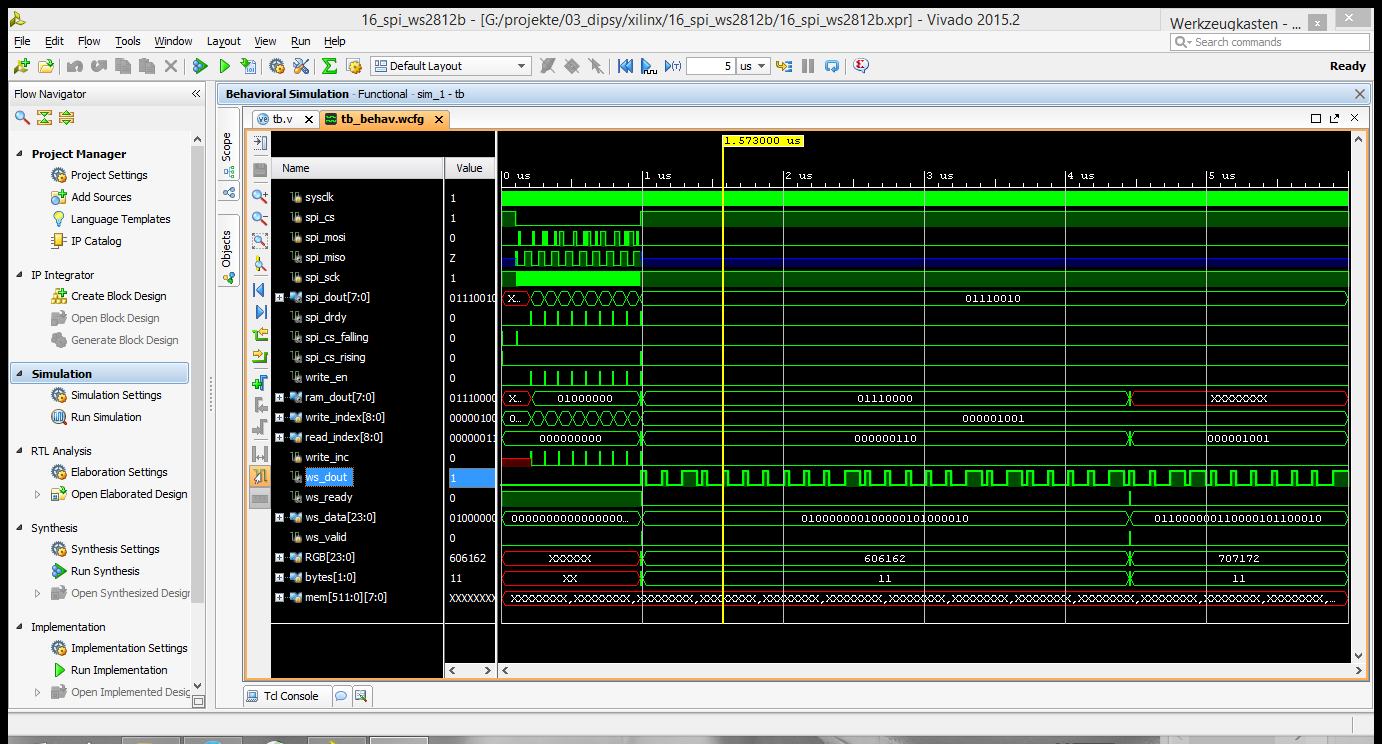

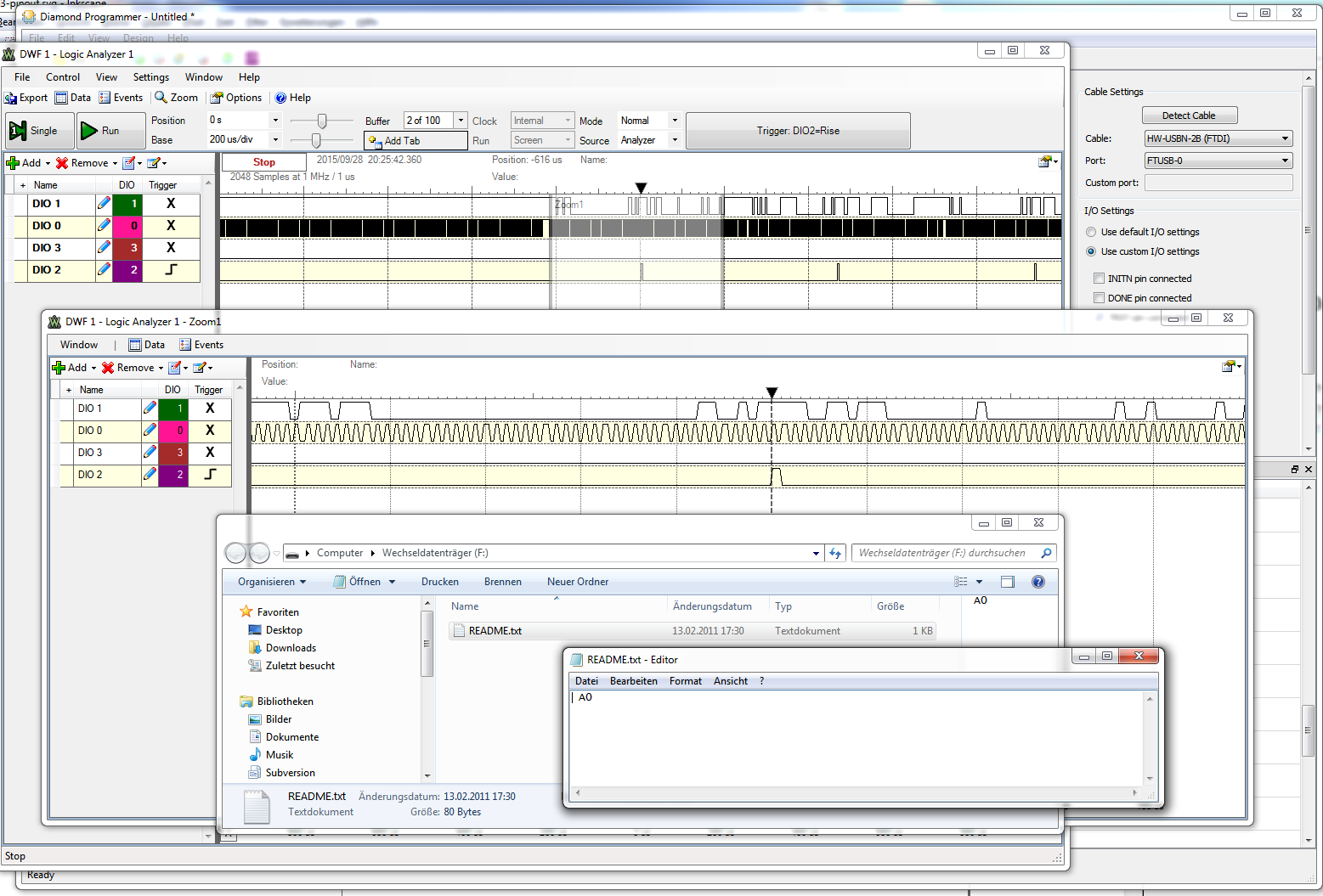

Compile your mixed Verilog/VHDL design with Lattice's iCECube 2 software. If you want you can also use other software (like Xilinx's Vivado) to develop and simulate you code first:

Do I need anything special to program it?

Absolutely not! A binary configuration for dipsy is less than 32 kB in size, so you can include it in your arduino sketch, or store it in an external EEPROM or SD card if your microcontroller doesn't have the extra flash space. dipsy can be configured with a simple SPI interface, and we even have an arduino library for that!

What if I don't use arduino?

No problem, it's easy enough to port to other environments and languages. We have tested dipsy with

- Raspberry Pi,

- BeagleBone Black

- Intel Edison

- Teensy 3.1 and LC

We're also working on a tool to program dipsy with USB<->Serial bridges.

The configuration is stored in

- volatile internal configuration memory,

- one-time programmable configuration memory,

- or an external config flash chip

See a WS2812B test in action:

We also have very basic examples, starting with the classic blinky, to get you started with this FPGA board!

Five grains of Sand

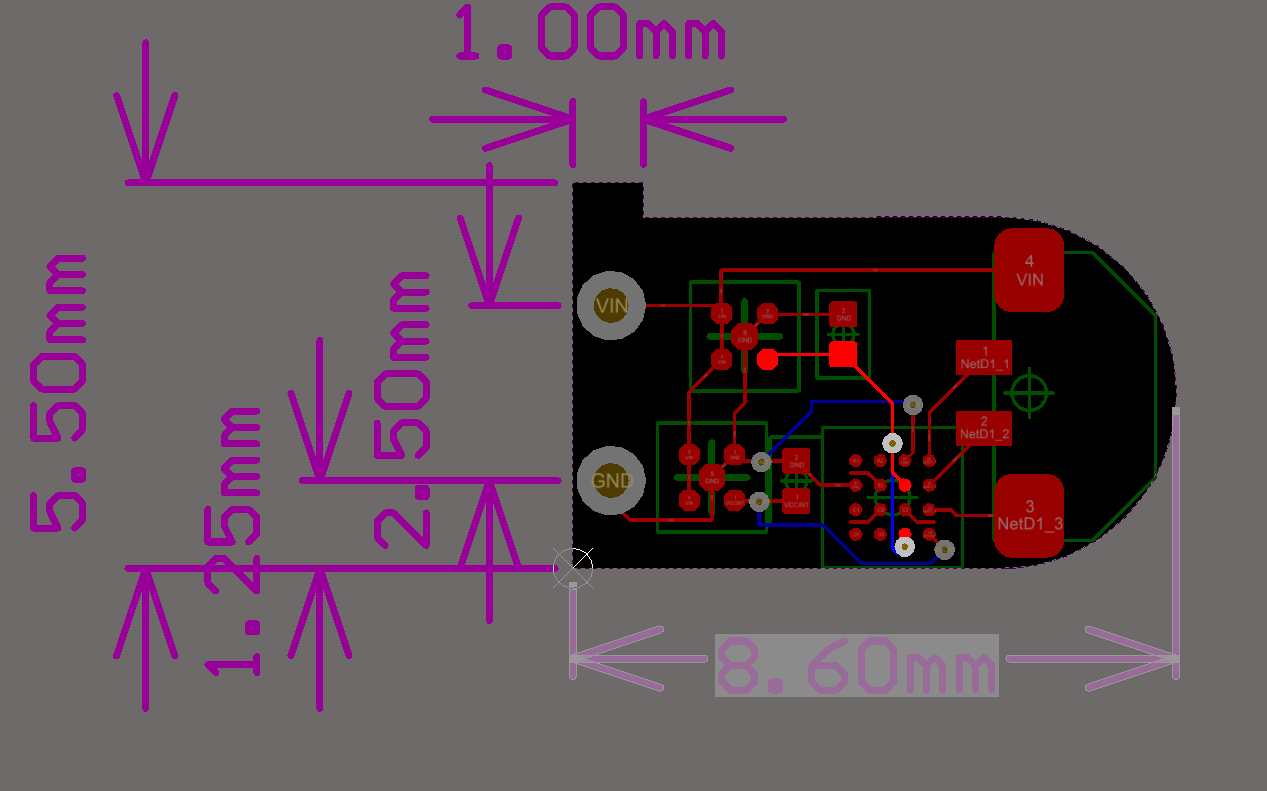

All components (FPGA, voltage regulator and three passives) on the dipsy PCB are smaller than 2mm. We give you those five grains of sand to

- Invent a new Processor Architecture and Instruction Set

- Design a System On Chip based on the architecture you invented

- Create a Computer or embedded system based on the SoC you designed

- Or just design a custom peripheral for your existing project

Take the task!

Do itNOW!

Bill of Materials

- Lattice iCE40UL1K-SWG16

- TLP713 LDO

- 2x Capacitor 1 µF 0402

- Resistor 10 K 0402

System Diagram

Licenses

CERN OHL- Hardware design (Schematic, PCB, Production files)

The hardware license is the most important one, there are many tools and utilities and IP Cores that may have different or undefined unknown license. It is not possible to document all those use cases.

As example, the set of tools that makes the open-source FPGA toolchain is a mix of MIT, GPL, Public Domain and "missing" licenses.

AVR Basic Compiler - is fully copyrighted by Antti Lukats, but has been released under several different Company names in the past, and possible will be released under some new...

Read more » Antti Lukats

Antti Lukats

jaromir.sukuba

jaromir.sukuba

Dave Vandenbout

Dave Vandenbout

Great work! Love it:) It is so tiny!