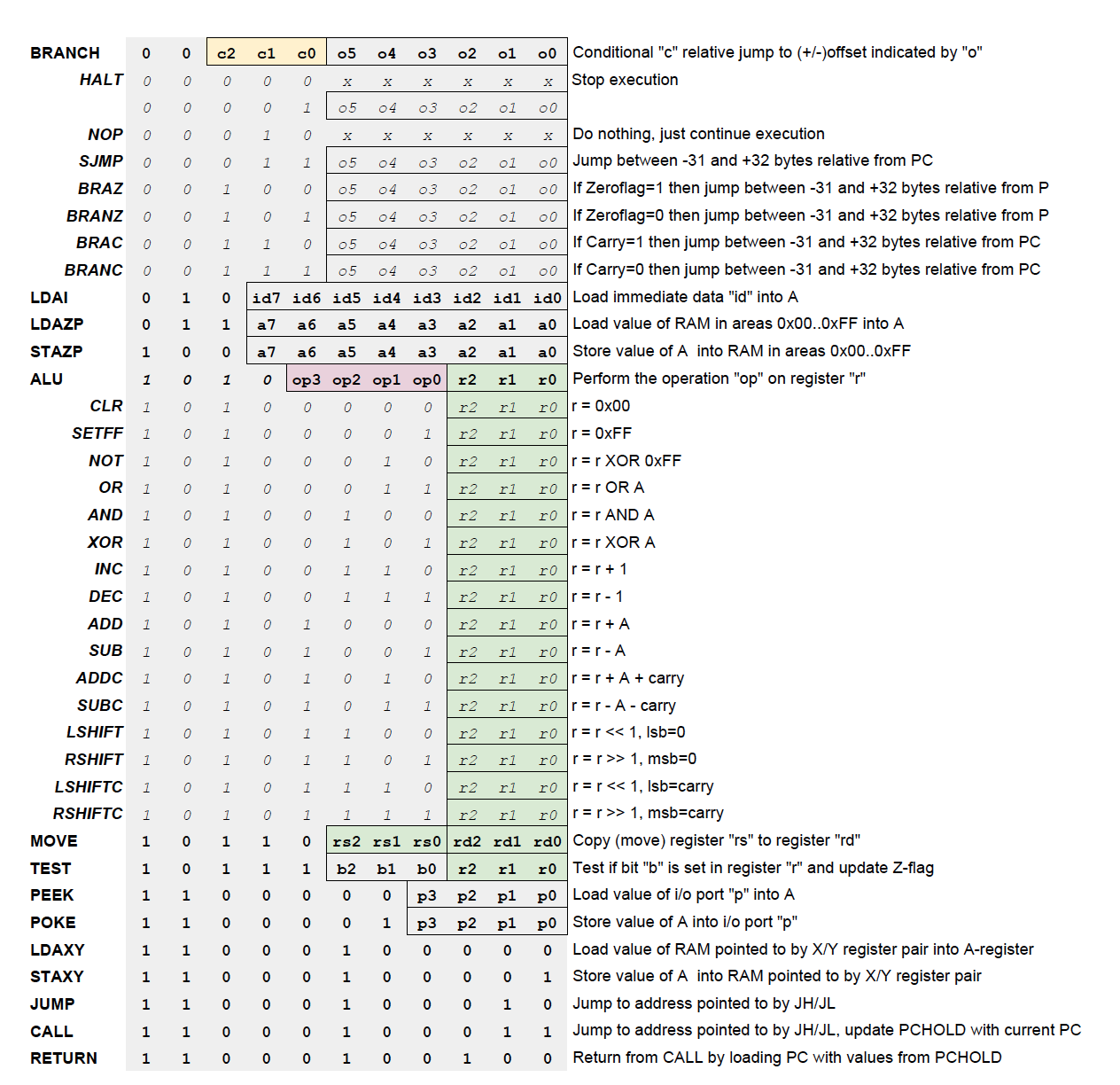

I've been thinking a bit of how the overall architecture and the instruction set should look like.

As it looks now I lean towards a Harvard architecture (separate data & program memories) and also separate I/O instructions.

I also want to do a single cycle CPU so each instruction needs to carry its full info/data in a single "instruction byte". This in contrast with for instance a 6502 processor where there are both 1, 2 and 3 byte instructions. For instance DEX=0xCA, LDA=0xA9 0x00, JMP=0x4C 0x00 0x00

To be able to do this reasonably effective on a 8-bit databus I need an instruction width of 11 bits.

I also plan to have 8 registers.

| A | Main working register/accumulator |

| B | General register |

| C | General register |

| D | General register |

| X | General register/High memory pointer |

| Y | General register/Low memory pointer |

| JH | High memory pointer for jumps/calls |

| JL | Low memory pointer for jumps/calls |

In addition to these there will be a 16 bit Program Counter, and a 16 bit Holding register for the Program Counter.

I just realized that I'm missing the SetCarry and ClearCarry instructions in the list below, I'll add them later - too lazy to make another screenshot and upload it again now :-)

matseng

matseng

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.