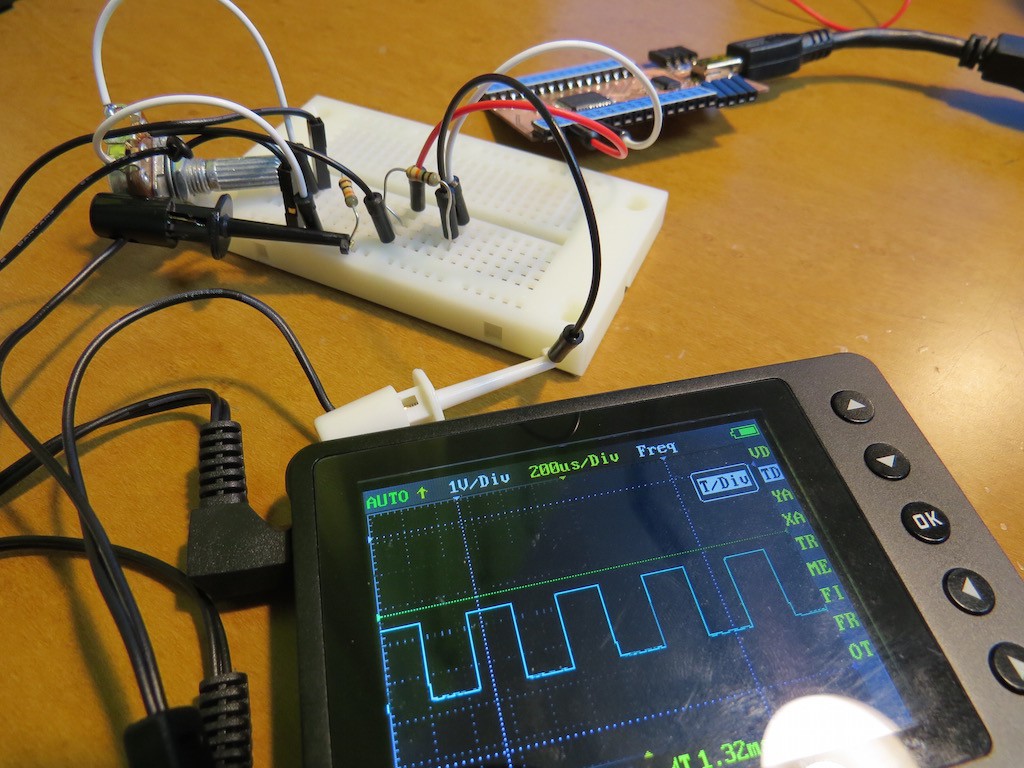

(Question 1) CPLD can organise RC oscillator?

Widely square wave generation is realised by 7404 or 7414 but is it possible by CPLD?

The answer is in the following movie..

(Question 2) CPLD can work as analogue amplifier??

It is well known that inverter in 7404 can work as analogue amplifier by putting proper feedback resistors. My question is, the inverter in CPLD can work as amplifier by proper resistor?

The answer was, NO! The inverting signal is generated by some "artificial" (I know it is not good word, but synthesized?) way, not by N and P channel complementary circuit and voltage feedback by resistor network does not work.

Have fun!

kodera2t

kodera2t

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Hah, I always wondered whether TTL could be used as an amplifier, and here you say it's "well known" ;)

Interesting experiments!

Are you sure? yes | no

I think that you would have answers if you read the datasheets :-)

Are you sure? yes | no

Interesting experiment. I used NS 16V8 GAL with resistor feedback (similar to CMOS inverters) as crystal oscillators a long time ago.

Is that using high power or low power setting for the macrocell? Low power is not going to work as the cell is powered down between signal edges, so that breaks the feedback.

Are you sure? yes | no

it is not high power but also not low power. Default setting, which seems 20mA driving..

Are you sure? yes | no

What I meant was high speed under "Macrocell Power Setting". (By default, "Macrocell Power Setting" is set to standard (Std), which is High speed. This means that the macrocell is always on. "Output Slew Rate" is set by default to "Fast" by default.) I don't see any settings that need to be changed from default.

I am guessing that they might have a schmitt trigger (with a lot of gain from positive feedback) at the input that cleans up and speeds up the input signals. That might prevent the part from being used as an amplifier.

Your observation are right, this part won't work as an amplifier.

Are you sure? yes | no

An interesting experiment. I would think it would very much depend on the actual device topology, implementation technology and fabrication, but I am wondering if you saw this article where they managed to make a ring-oscillator in an FPGA (which changes frequency based on physical stress)? http://hackaday.com/2015/09/27/mystery-fpga-circuit-feels-the-pressure/

I wonder if this Verlog (or something like it) can fit in your CPLD? :-)

Are you sure? yes | no

I guess similar thing may happen! (I am not sure but depends on physical arrangement of chip in package, and relation of stress and distortion, which will make some permeability or some parameter change). Anyway extreme!

Are you sure? yes | no