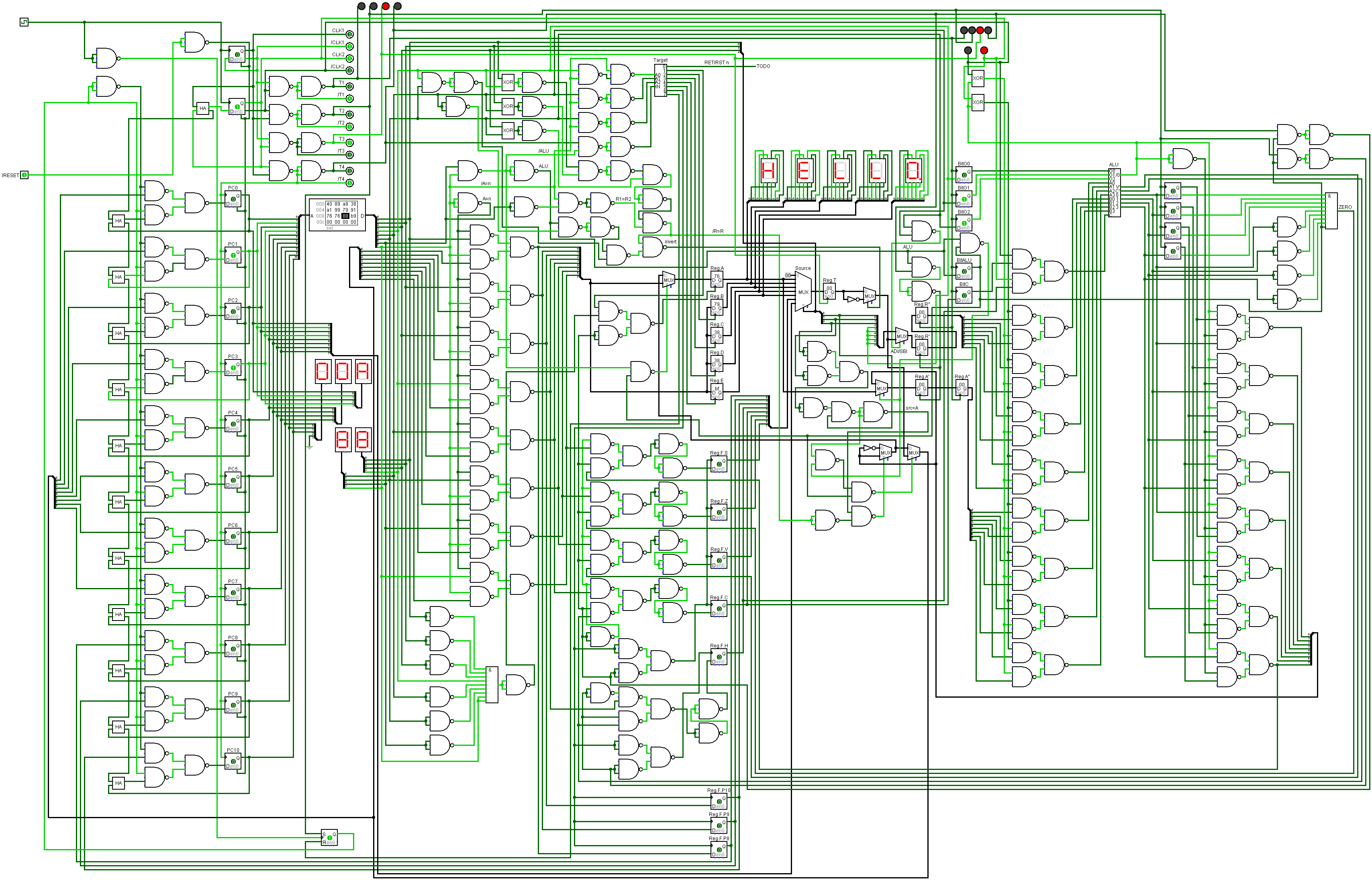

Simulation of all straightforward commands is ready (everything except RST n, RET, SAEFF and SANFF that require special treatment) with both pipeline stages (2nd stage is having 4-bit ALU that works sequentially in 2 steps to handle 8-bit data). The only special command added is NOP (0x88) and 0xBE,0xBF are still G=F,G=~G. Let's call this subset "NEDONAND lite" - it's pretty much usable even in this state, because bunch of edge-cases mentioned in previous log post was already handled - see Logisim screenshot:

Interesting thing is that in order to integrate 4-bit ALU (that itself consists of 30 chips 74F00) I added muxing-demuxing logic that consists of about 20 chips 74F00 or 66% of ALU, so it's just a little less than adding 2nd 4-bit ALU in parallel to achieve 8-bit operations. Another observation - having instructions that executed in different stages of instruction pipeline (some in 1st as register copying and some in 2nd as instructions with codes 11xxxxxx that use ALU) is very tricky and require precise edge-case analysis and handling in hardware...

P.S. Expected waveforms for actual hardware (should be slow enough to work with 2716 ROM):

_________________

/RST ______|

______ _ _ _ _

CLK |_| |_| |_| |_| |_ 6.666 MHz

______ ___ ___

CLK1 |___| |___| |_ 3.333 MHz

______ _______

CLK2 |_______| |_ 1.666 MHz

1st stage of pipeline (fetch and decode + simple execute):

__________ _

/OE |___________| 450 ns

. ___ .

REGRD _____________| |_____ 150 ns

. . ___

REGWR _________________| |_ 150 ns

| 300ns | 300ns |

^ ^

| 450ns |

| \data ready

|

\address ready

2nd stage of pipeline (complex execute through ALU):

_______ .

HALF1 _____| |_________ 300 ns

. ___ .

ASTO1 _________| |_________ 150 ns

. _______

HALF2 _____________| |_ 300 ns

. . ___

ASTO2 _________________| |_ 150 ns

| 300ns | 300ns |

P.P.S. If you want to play with it you may download Logisim file from a file storage: nedonand.circ

SHAOS

SHAOS

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.