Debugging

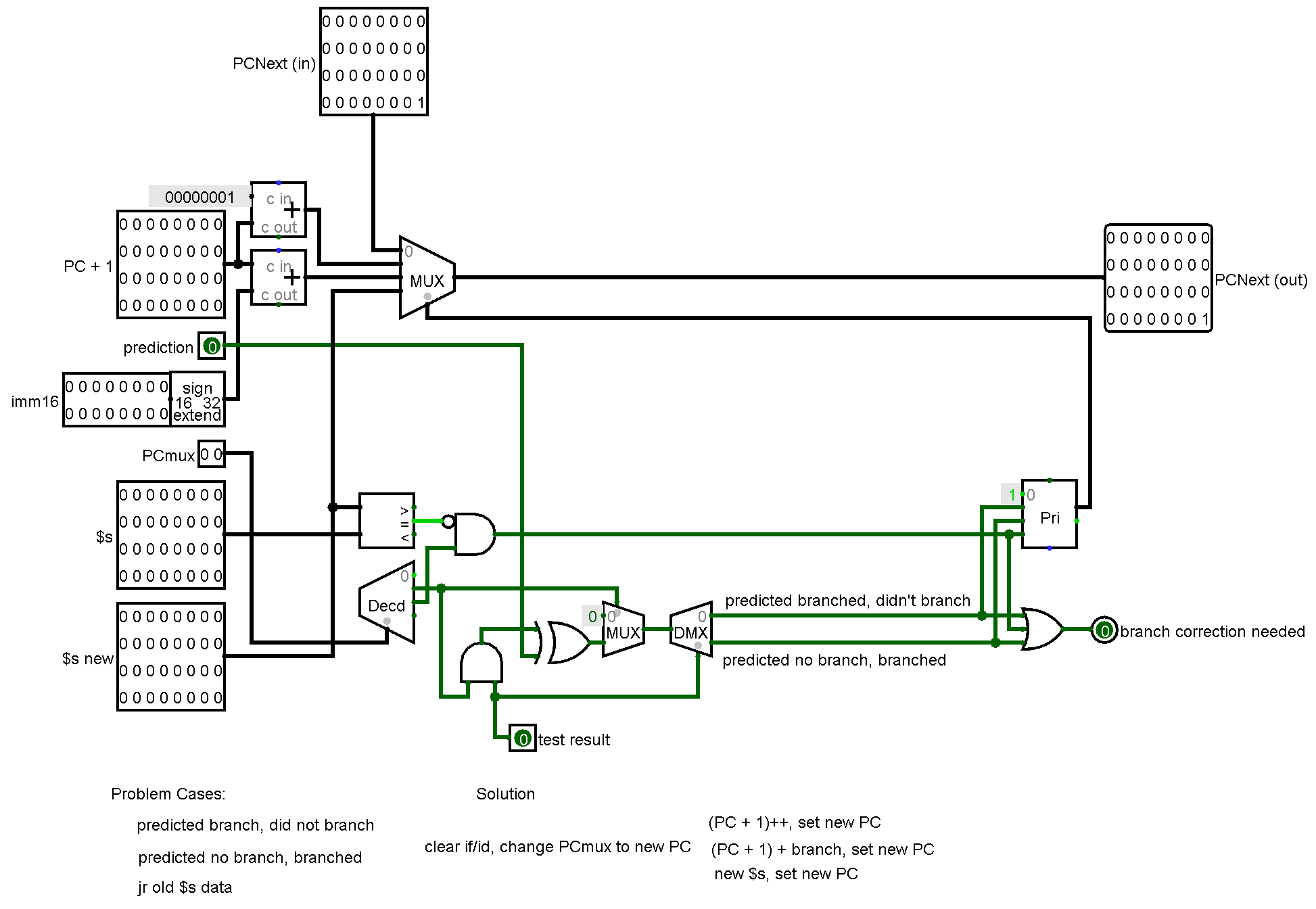

As I was running some test code, I discovered that stale register data was being used to execute the jump register instruction. The fix for this was simple; I added a "new $s" signal from the forwarding registers to the branch correction. In addition, I also tidied up and simplified the branch correction.

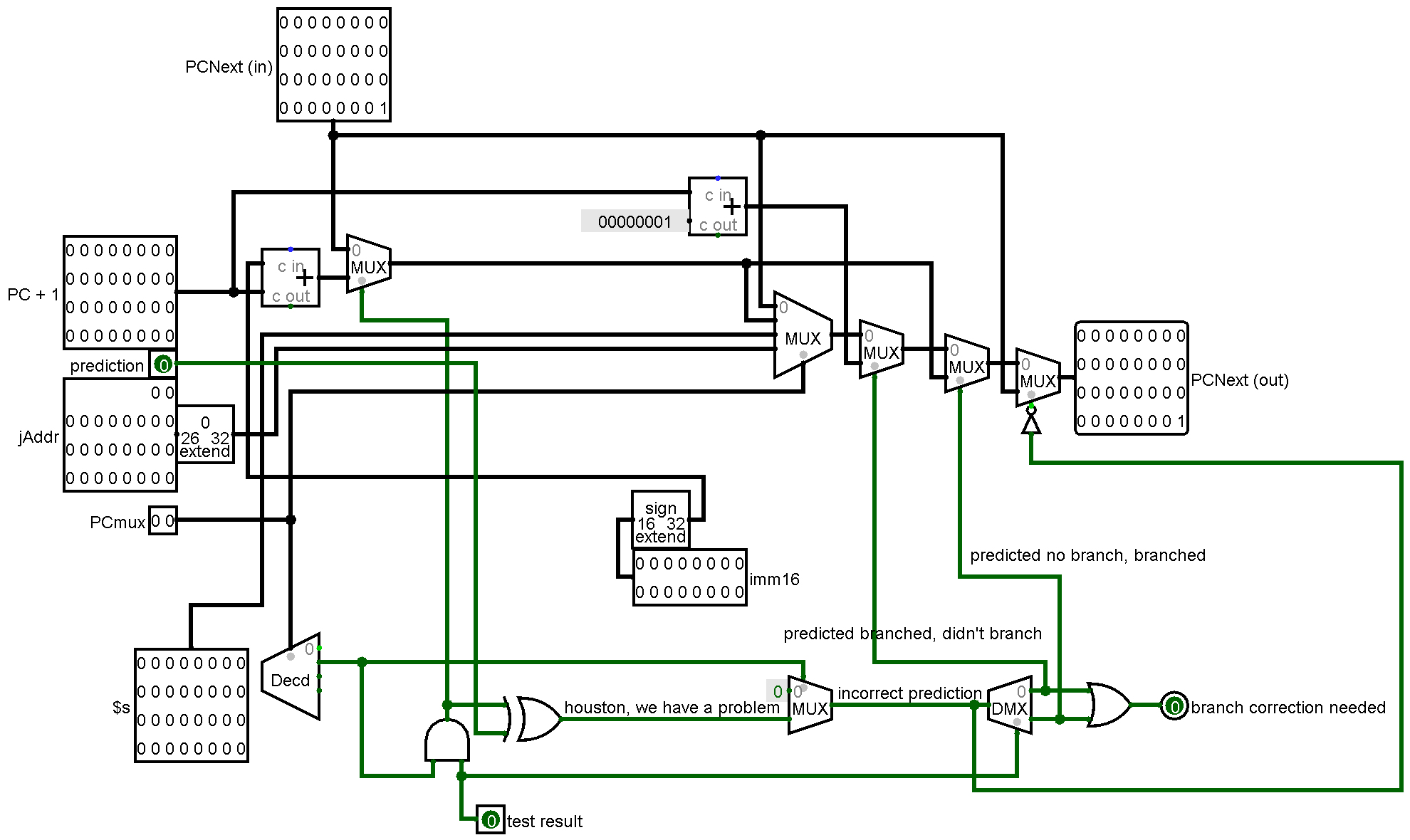

Old Branch Correction

New Branch Correction

This simplified design is not only easier to understand, but it is also faster because there is no longer a chain of multiplexers that the "PCNext" signal has to propagate through.

Reed Foster

Reed Foster

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.