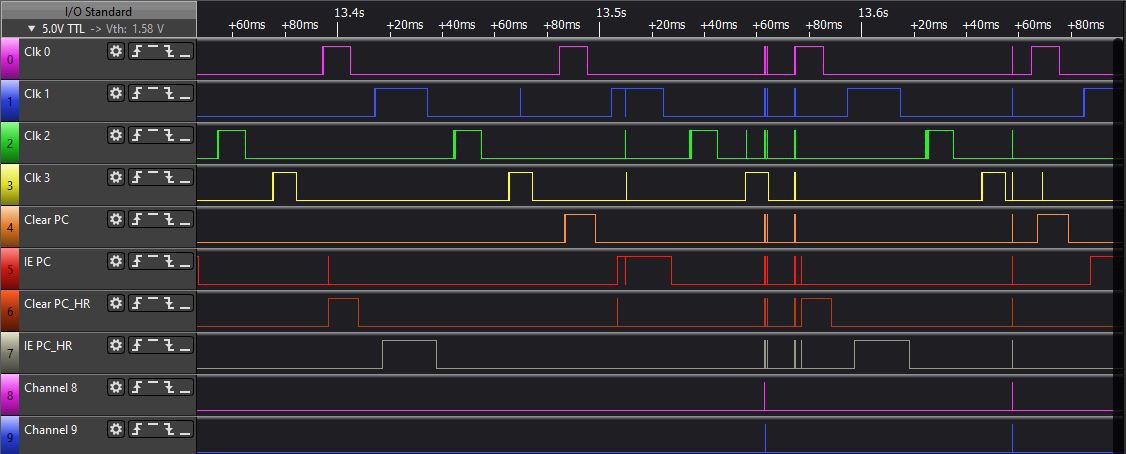

So, here you see the first logic analyzer picture...

The NOP command starts at position 13,4 sec with the Clk 0. Clk 0 is the timeslot when all registers which are written in this cycle are deleted. So the PC_HR register is deleted during Clk 0, it is written during Clk 1. Clk 2 and Clk 3 are used for the internal state machine of the control unit.

The next Clk 0 impuls starts the second part of the NOP command. The PC itself is deleted during Clk 0 and written during Clk 1.

During the next days i will add additional control lines, but the results are very promising until now.

Peter

Peter

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.