Join the Hack Chat by clicking on the JOIN HACK CHAT button. Then, request to join #Hack Chat.

Don't request to join from this page, click the JOIN HACK CHAT button.

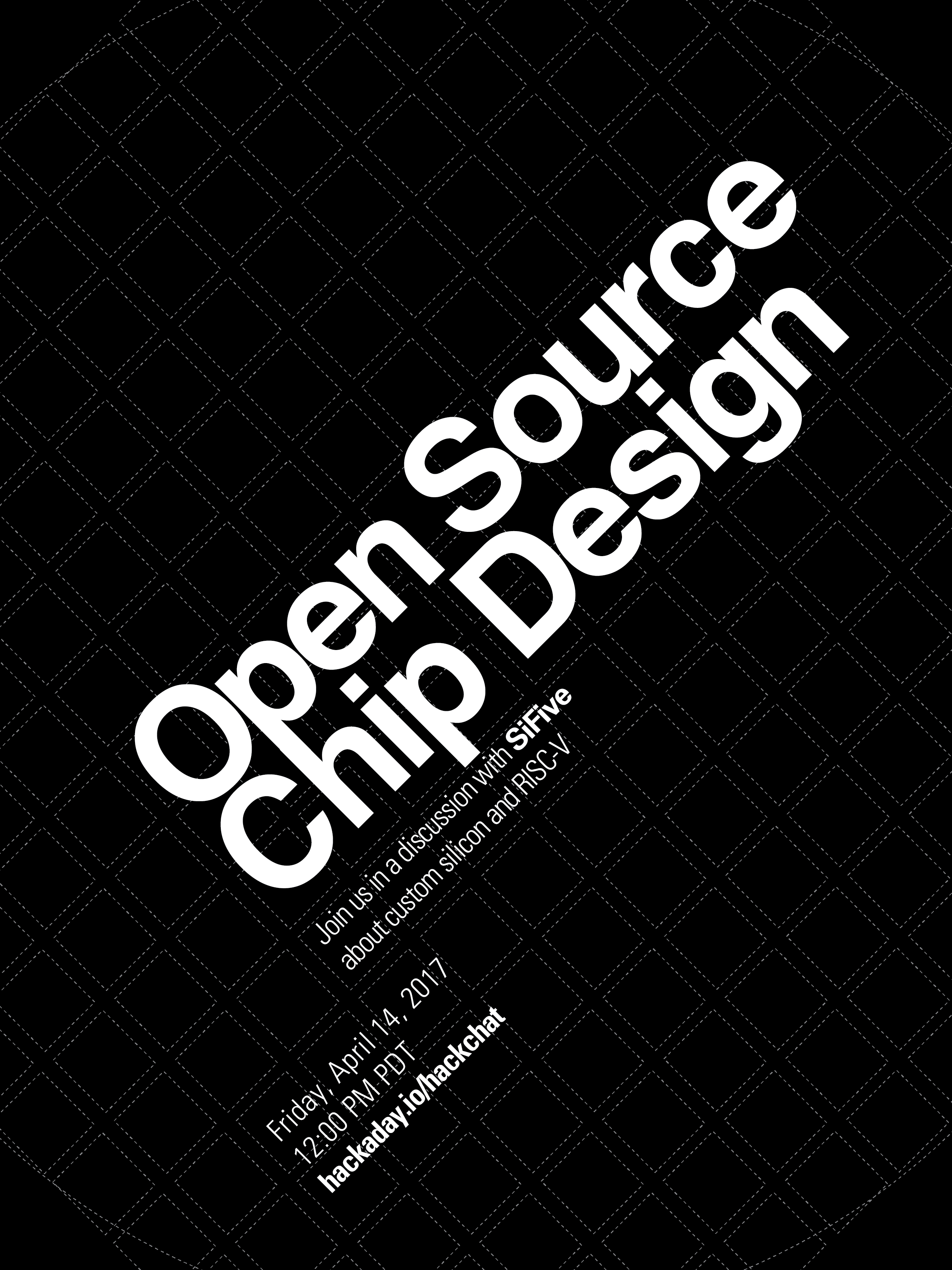

Come hang out for 30 or so minutes and talk to Jack Kang, VP of Product and Business Development at SiFive. Join this chat to learn about RISC-V, the free and open Instruction Set. Ask questions about what it means to have open-source chips, and how SiFive plans to help everybody—from the smallest company, inventor, and maker, get access to custom silicon.

About @Jack Kang :: Jack started his career as a frontend design engineer, with a focus on CPU architecture and design. Jack received his BS degree in Electrical Engineering and Computer Science from UC Berkeley.

About SiFive :: SiFive was founded by the creators of the free and open RISC-V architecture as a reaction to the end of conventional transistor scaling and escalating chip design costs. SiFive believes that by enabling the power of open-source hardware design, custom silicon is available to everyone, enabling a whole new range of applications.

We're meeting in the #Hack Chat on April 14th, noon PDT.

Here's the list for discussion and questions, add yours to the sheet!