Update: CKE + /CS synchronization notes (at bottom) And More!

PROTOTYPING:

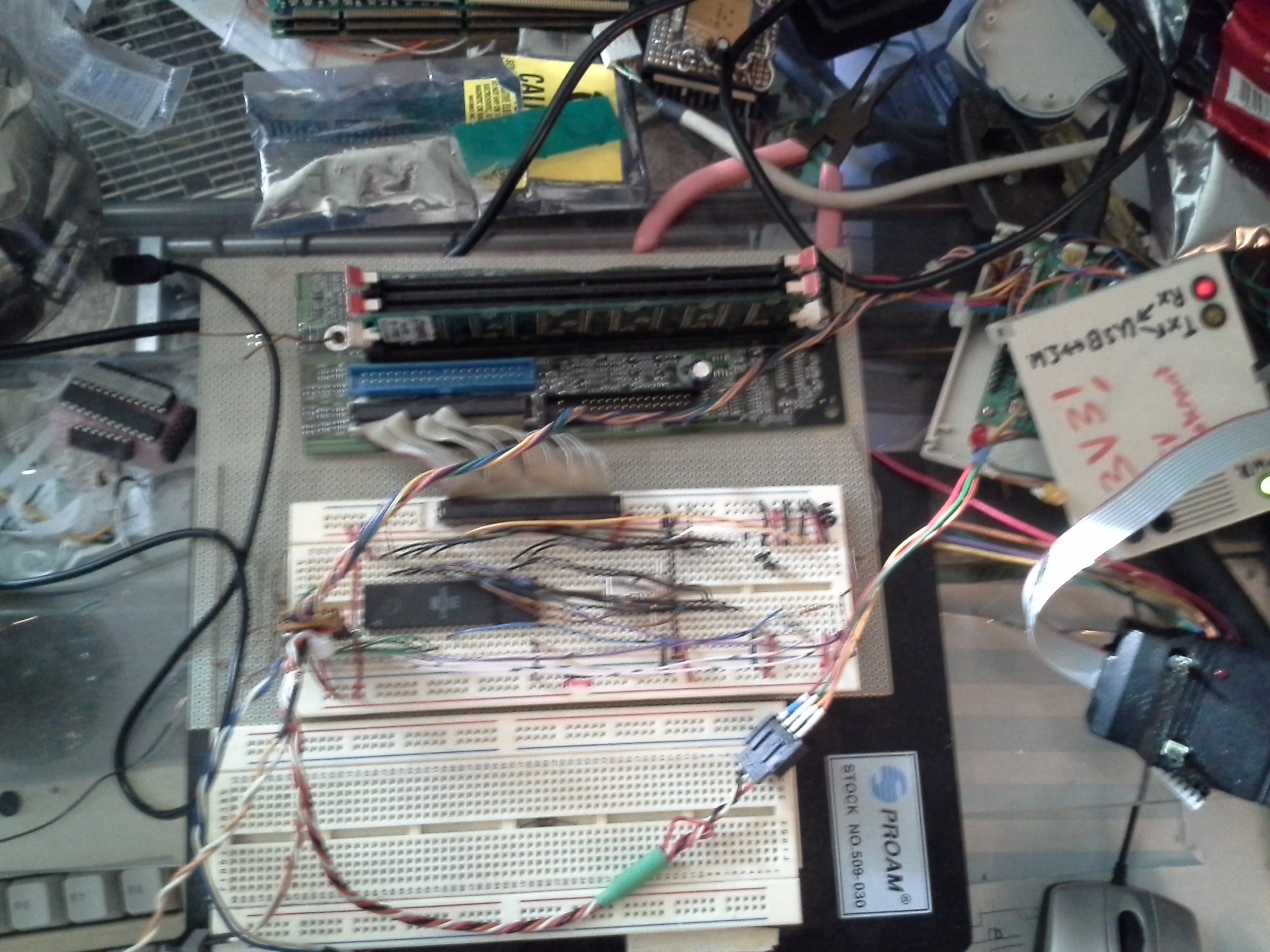

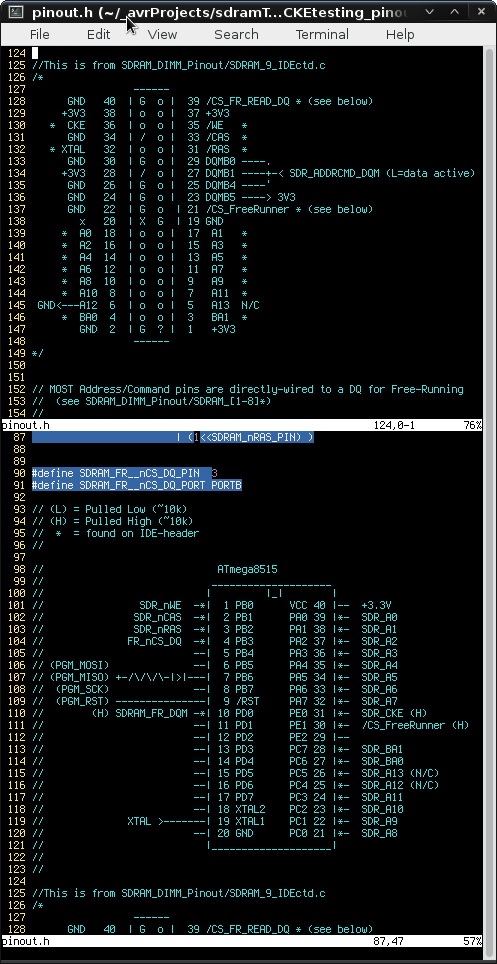

Stupidly, I threw the details in the "Instructions"... but anyways, I decided to use an old motherboard's DIMM sockets for this prototyping-stage this time 'round. I cut the mobo down to just the DIMMs and the IDE/Floppy connectors, removed all the components, and wired up the back-side. One IDE-connector has *just enough* available pins for the "Free-Runner." The breadboard is one I hacked-together long ago, mapping a 40-pin dual-row connector to the right side breadboard terminals.

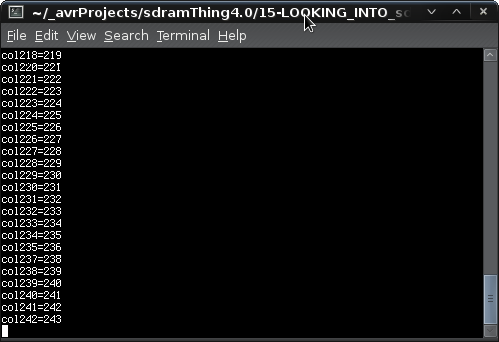

CKE-Tested

The first prototype is now running... This is a big moment, it's verifying that CKE works as expected, and it seems to be doing-so "swimmingly"!

This, again, is a big moment... CKE is what makes it possible to have a host running asynchronously with the SDRAM's clock. No more requirement for tightly-tuned Assembly instructions! No more counting (and accounting for) exactly how many CPU-cycles it takes between one rising-edge and the next... It's amazing!

(Seriously, that shizzle was *weeks* of work for the previous iterations).

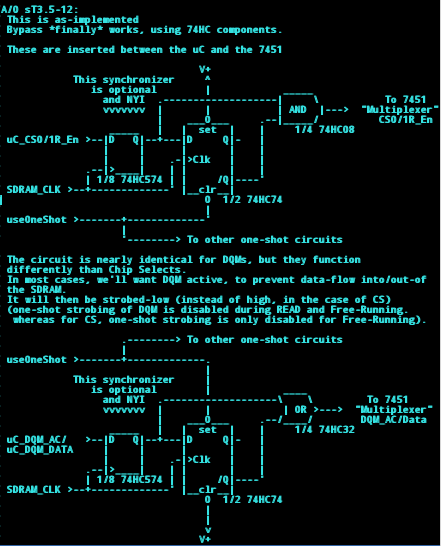

It will require two (three?) one-shot circuits... One for the CKE pin, and another for the Chip-Select(s). These are pretty simple and have been described in various places here and at #sdramThing4.5 "Logic Analyzer"... They basically boil down to two flip-flops (or D-Latches) and a gate. What they do is to take the "Host"'s comparatively slow GPIO "strobe" signals and make them one single SDRAM-clock width.

In: _______--------____ Out: ________-__________

That's been well-tested in sdramThing4.5... Since the clocks were synchronized (albiet different speeds), I was able to get away with a single latch, but now that the clocks won't be synchronized, an additional D-latch is a good idea, just to make sure everything aligns as expected.

Oh, and no more DQM-one-shots, so that's cool.

There's still this idea floating in the back of my mind that maybe I can get away without /CS one-shots... But I can't quite wrap my head around it. And, further, there's explicit mention in the datasheets that many of the hacks I'd attempt would cause "undefined" behavior... So, while it might work on one brand/make of chip, it might not on another...

(Yes, this CKE-Testing and later prototypes are still being done with an AVR... I simulated the one-shot strobe on CKE (and CS) with a GPIO and identical clocks just to make sure it works as-expected, soon I'll move on to the one-shot circuits. Kinda ironic, as this prototype is, now, basically at the level of sdramThing2.0... it's like reinventing the wheel, but with some hindsight and a LOT of code-examples to work from and improve-on).

Instructions

If you haven't noticed, I've been putting up "Instructions" as I've been throwing together the first sdramThingZero prototype. Check 'em out, but don't build one using those instructions until I've had some time to get some funkiness in the instructions worked out (unless you want to be a beta-tester! Lemme know!).

Serial Presence Detect

For some reason I had it in my mind that it would be possible to put this together without knowing the intricate-details of the SDRAM-chips... But it occurs to me, now, that it's necessary to know the number of columns in a "page" for various reasons. I suppose there are various ways of figuring this out (maybe even just by reading/writing to the chip and seeing what data comes back?) But the obvious way is to read the serial-presence-detect EEPROM... So, I'll be mulling that over a bit. Could probably bit-bang I2C through the same bus as everything else... but that's more chips, and maybe that's not necessary. We'll see. (Surely, somehow they managed to auto-detect the RAM topologies back in the day before SPD existed... Remember the ol' 30 and 72-pin SIMMs?).

Update: CKE+/CS Synchronization Mwahahahaha!

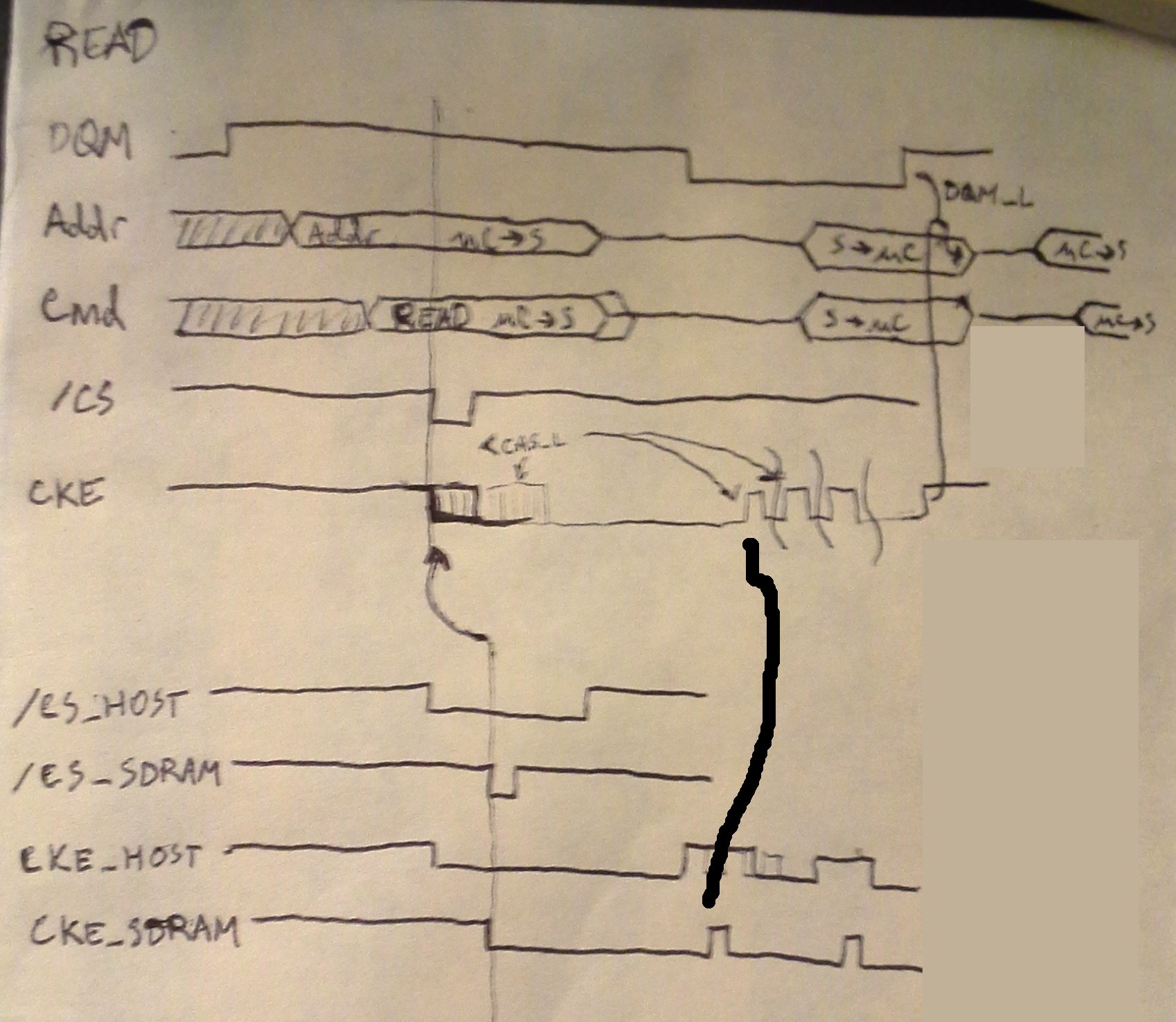

Yah see it? (ignore the heavy black line, it's not the point)

Yeahp... So, for read-back (and write) there comes a moment where we need to have the /CS strobe synchronized with the CKE switching from Clock-Enabled to Clock-Disabled/One-Shot mode.

Technically, it could occur a few SDRAM clocks *after* (but not before) the /CS... actually, any number, but that number needs to be known. Probably easier to sync their edges.

So, maybe those one-shots will be a bit more complicated now...

Bah! Not complicated at all...

First things first: Put CKE and CS inputs (As well as the One-Shot Enable input), from the host, on the same port/register... That way they load simultaneously (done, we need to load things into registers anyhow, since our bus-width for sdramThingZero is much smaller than the number of I/Os on the SDRAM).

Then, simply, add a D-latch (delay) between the one-shot-enable output from its register, and the 7474's Clear input.

Oh, and that "additional D-latch ... just to make sure everything aligns as expected" maybe is already taken care of by those "bus expander" registers.... hmmm...

Eric Hertz

Eric Hertz

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Whoo hooo! Nicely done! And I LOVE how well you are documenting all this. I can even more or less understand it. Just lovely!

Are you sure? yes | no