I had to undo the last change to the ALU, because it broke things.

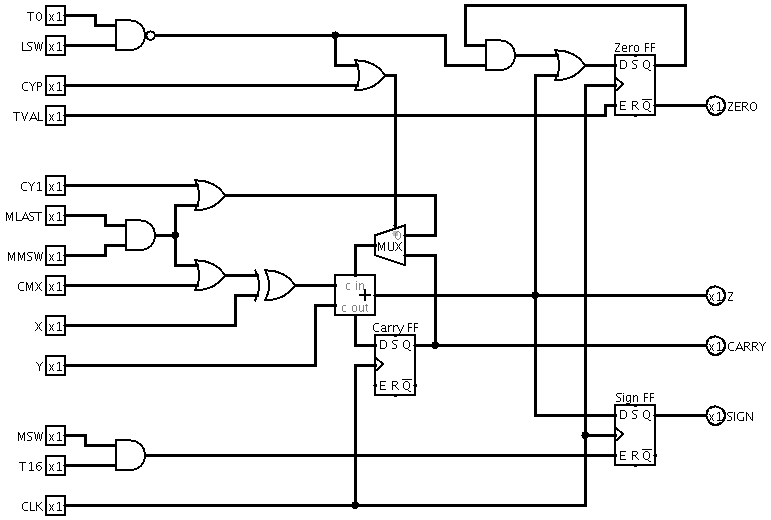

The ALU, and also the right-shifting mechanism, need to work on full 18-bit words with the sign bit in bit 17, to accommodate a one-bit overflow of intermediate results during multiplication. As long as the final results of arithmetic operations don't overflow, bits 16 and 17 should be the same, but there are ways for them to become different, which can lead to the Zero FF being set incorrectly.

To fix this, I did two things:

1. In the ALU, the Zero FF is not updated during bit 17.

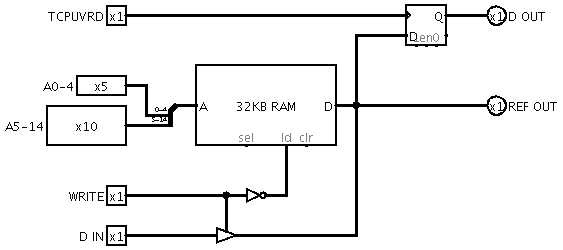

2. Bit 17 is forced to be the same as bit 16 when reading an operand from memory. This is done by a transparent latch after the output of the RAM that is frozen during bit 17 of an MSW. (A separate output is taken directly from the RAM for display refresh, so that the actual memory contents can be seen).

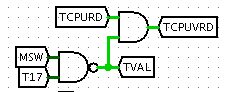

Two new timing signals are derived for these purposes, TVAL (Valid Bit) and TCPUVRD (Valid Bit during CPU Read cycle).

New ALU subcircuit:

New ALU subcircuit:

New main memory subcircuit:

New main memory subcircuit:

Fixing bit 17, more properlyish

A project log for BREDSAC

Electronic Dynamic Storage Breadboard Computer

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.