An excellent explanation of Integrated-Injection Logic (I2L) is in the classic IEEE paper from R. A. Pedersen of Bell Labs. In the early 1970s, MOSFET logic had not evolved into the high-speed technology that NMOS in the mid-late 1970s and CMOS in the early 1980s would become. One promising development is that of I2L, which offered the speed of TTL with much lower power-use, as well as a very simple silicon topology that lent itself well to large-scale integration.

Given the excellent explanation of I2L in Pedersen's paper, I won't attempt to explain I2L operation here.

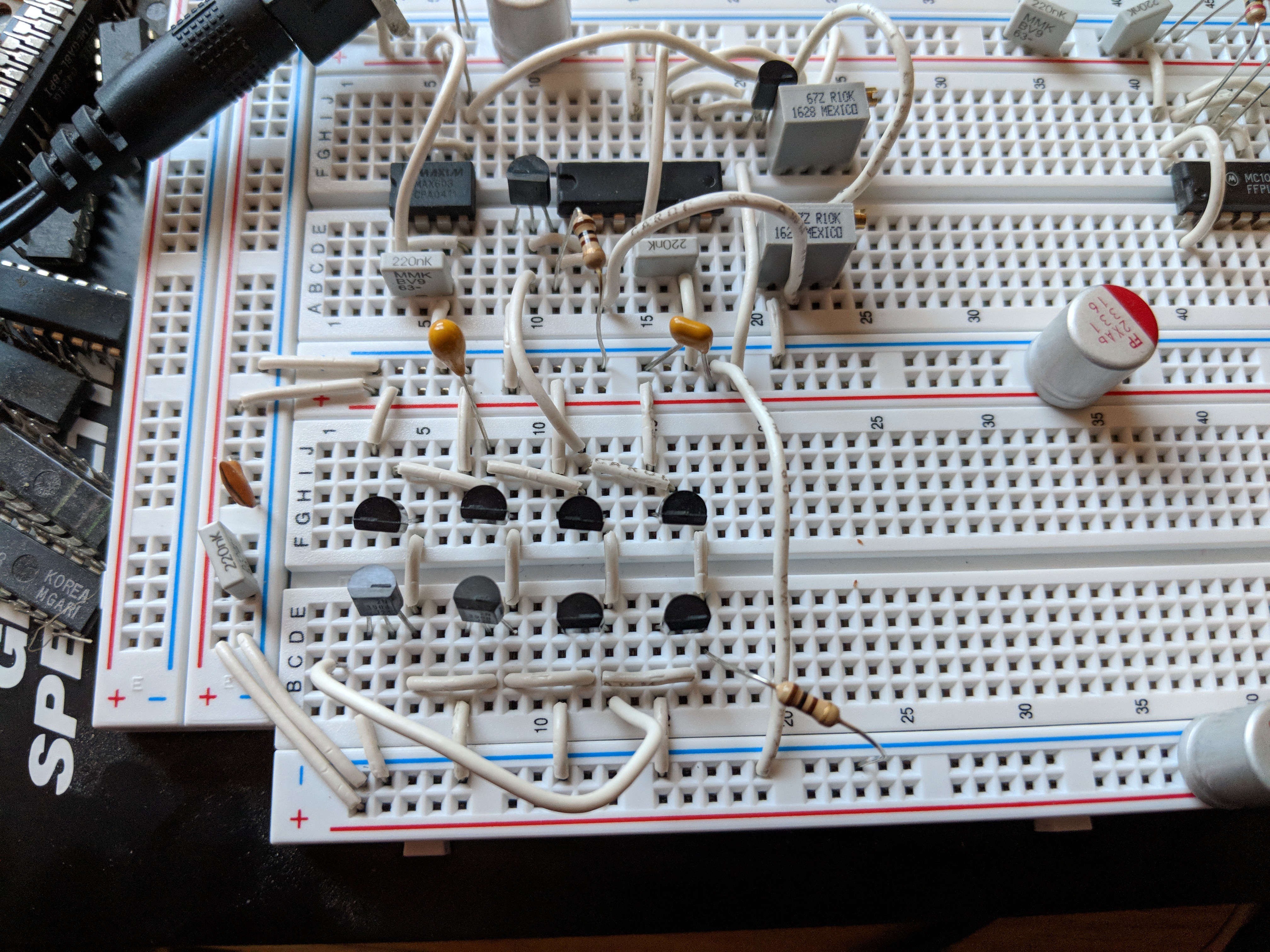

Instead, here's the LTspice circuit of a simple 3-inverter I2L ring oscillator.

Simulation with ON Semi models suggest operation frequency around 38MHz; subsequent simulation adding 5pF to each collector-node suggested a realistic proto-board frequency around 32.3MHz.

Circuitry to the upper-left is a 1V power-supply regulator and a bias-voltage generator for the PNP current-injectors. Adjusted for 2.6mA injection, the circuit operates around 30.9MHz - remarkably close to the simulation value! This is roughly 5.4nS propagation delay per inverter, with a speed-power product of 14pJ (this is considerably higher than ~1pJ of actual monolithic I2L where the transistors are optimized, but quite a bit better than 100pJ of standard TTL in the early 1970s).

Monolithic I2L merges the PNP current-sources with the NPN switches, making it compact.

It occurs to me to look for low-voltage, low-power transistors that more closely match the characteristics of the monolithic transistors used in classic I2L to see if I can get the speed-power product down to 'classic' levels.