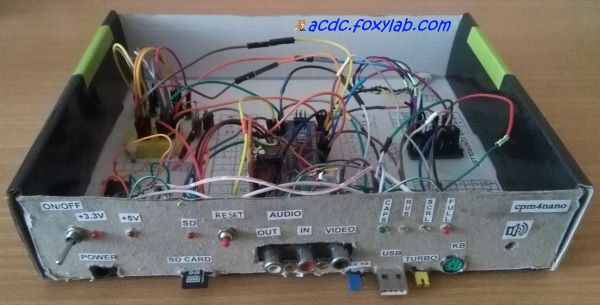

I did a redesign of the project, now it looks like this:

Evaluated the influence of the size of the instruction cache on the real speed of the "nanocomputer" operation using the example of the speed of thinking the first move by the machine in MICROCHESS (results for the TURBO mode, the video image was not drawn):

- without cache - 291 seconds;

- 4-byte cache (too small, overhead does not pay off and degrade speed) - 580 seconds;

- cache 8 bytes (optimum) - 21 seconds !!!;

- cache 16 bytes (too large, the overhead does not pay off) - 26 seconds.

Alexey Voronin

Alexey Voronin

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.