There are two ways to get to the Z80 bus for external operations.

- RESET* - Clears PC and sets address/data bus to Hi-Z

- BUSREQ* - input - Address, Data, MREQ*, IORQ*, RD*, WR* to HiZ

- BUSACK* - output indicates that BUSREQ* signal was performed (Hi-Z busses)

Other controls:

- HALT* - output

- A0-A15 - tristated by RESET*

- D0-D7 - tristated by RESET*

- BUSACK* - output

Debugging with Logic Analyzer

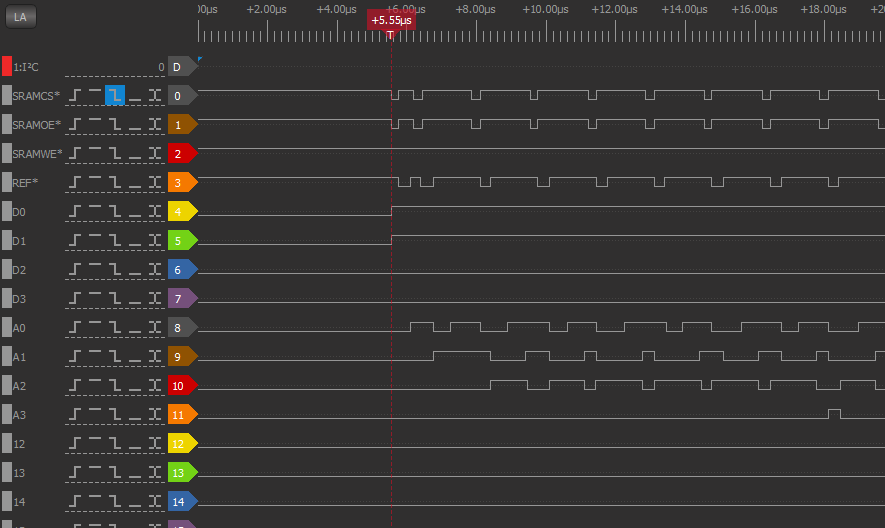

Looking at the lower address and data bits with the DSLogic+.

The data looks like the bottom nibble is stuck with 0x3 which does match the first instruction but it doesn't look like it's changing for the following instructions. Here's the first few lines of the assembly code:

unsigned char monitor_eprom[] =

{

0xF3, 0xC3, 0x8A, 0x01, 0x00, 0x00, 0x00, 0x00, 0xC3, 0x24, 0x01, 0x00,

0x00, 0x00, 0x00, 0x00, 0xC3, 0xC0, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00,

The first two instructions do have 0x3 as the bottom nibble but the next lines don't. The start of the code has:

MON .ORG $0000 ; MONITOR ROM RESET VECTOR

;------------------------------------------------------------------------------

; Reset

;------------------------------------------------------------------------------

RST00 DI ;Disable INTerrupts

JP INIT ;Initialize Hardware and go

NOP

NOP

NOP

NOP

Looking at the Code

I want to look and see if the right stuff is running, but I don't have a listing file for the output of the assembler. I just have Grant's ASM source. Grant also includes the TASM assembler but it doesn't run under 64-bit windows.

I tried TASM in DOSBOX and it works. It needed all the files (TASM.*). I did that and the program created a list file automatically. Here's the first few lines of the listing:

0102 0000 F3 RST00 DI ;Disable INTerrupts 0103 0001 C3 8A 01 JP INIT ;Initialize Hardware and go 0104 0004 00 NOP 0105 0005 00 NOP 0106 0006 00 NOP 0107 0007 00 NOP

INIT is:

0387 018A 31 AE 40 INIT LD SP,STACK ; Set the Stack Pointer 0388 018D 0389 018D 21 00 40 LD HL,serABuf 0390 0190 22 40 40 LD (serAInPtr),HL 0391 0193 22 42 40 LD (serARdPtr),HL 0392 0196 0393 0196 21 45 40 LD HL,serBBuf 0394 0199 22 85 40 LD (serBInPtr),HL 0395 019C 22 87 40 LD (serBRdPtr),HL 0396 019F 0397 019F AF xor a ;0 to accumulator 0398 01A0 32 44 40 LD (serABufUsed),A 0399 01A3 32 89 40 LD (serBBufUsed),A 0400 01A6 0401 01A6 ; Initialise SIO 0402 01A6 0403 01A6 3E 00 LD A,$00 0404 01A8 D3 02 OUT (SIOA_C),A 0405 01AA 3E 18 LD A,$18 0406 01AC D3 02 OUT (SIOA_C),A

Dumped the RST00 and INIT code with the Front Panel and the code matches the listing so I think it loaded correctly.

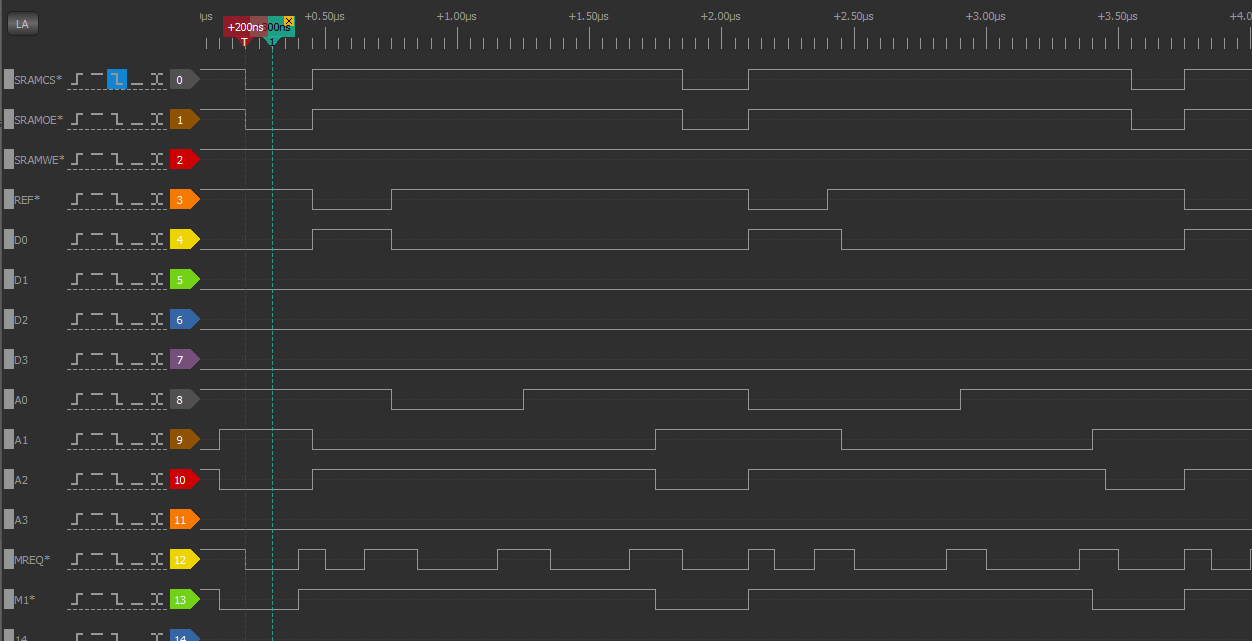

Added connection to M1* and MREQ*. MREQ* runs a lot more than I expected but it's not always qualified with M1*.

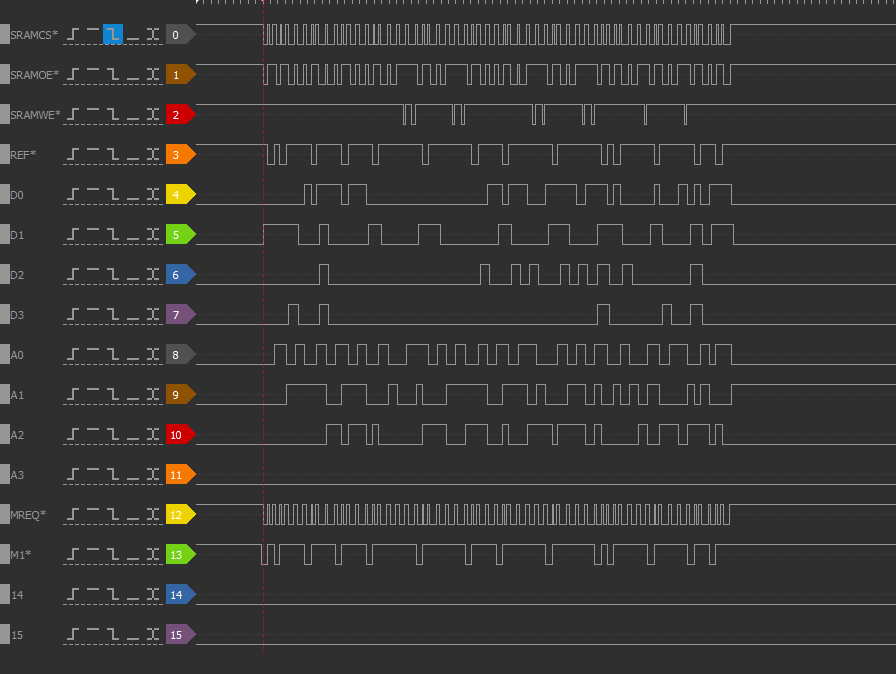

I found the problem - it is in the trace above. I was qualifying SRAMCS* with M1* being low. M1* is only low during the first byte of an instruction, ie, it's only active during the opcode fetch. I removed M1* from the equation and got this:

And IOREQ* is stuck low waiting on the PSoC to remove the WAIT*. The code runs about as long as I would expect given the number of instructions shown to reach address 0x01A8 where the IO OUT happens.

Confirmed that IOREQ* is low with the scope. First time I've seen it low!!!

Now, on to work on the SIO emulator...

land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.