The majority of the time the Z80 is reading/writing SRAM. The SRAM is a 55 nS part and runs with no wait states. I/O is slowed down by reality (serial data rates are much slower than CPU times). However, it is interesting to see what differences there might be between emulated I/O and I/O performed by dedicated chips.

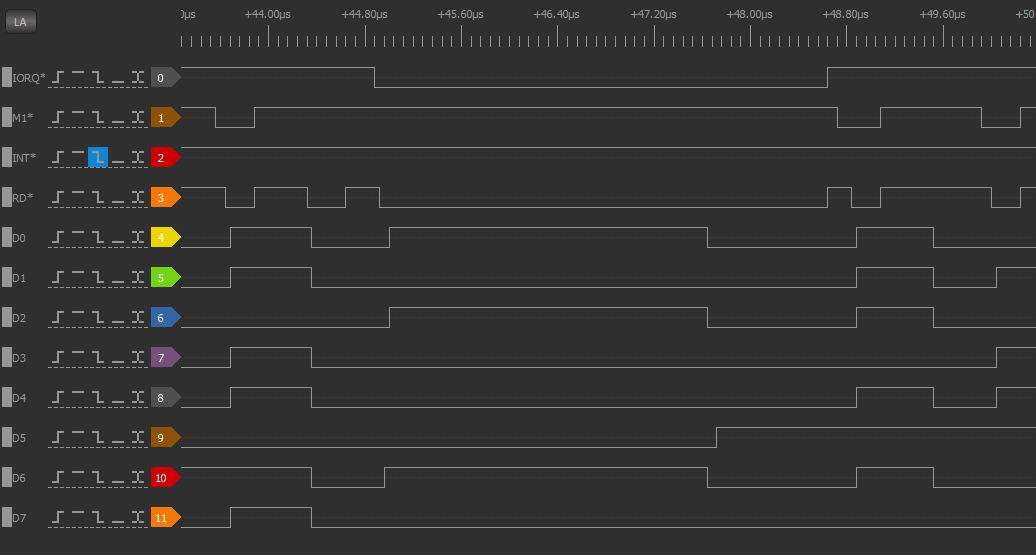

I/O Timing is somewhat variable since the I/O (currently) is done by the PSoC polling the IO interface to see if WAIT* is active. Here's one typical read cycle time of about 3.8 uS.

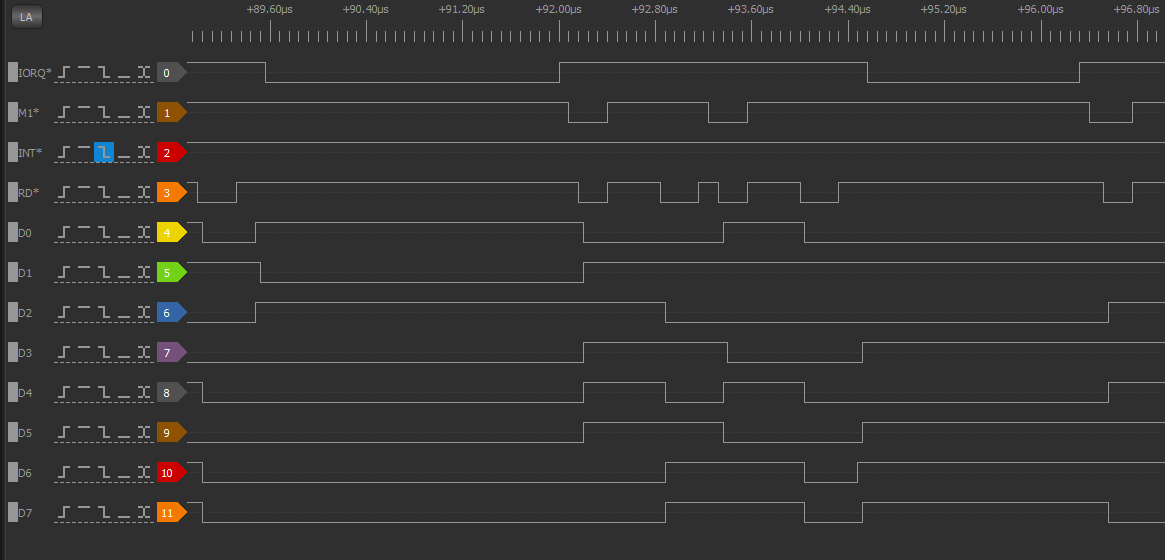

SIO control register reads consist of a write to the register number followed by a read from the selected SIO register. The time for both accesses is 6.8 uS.

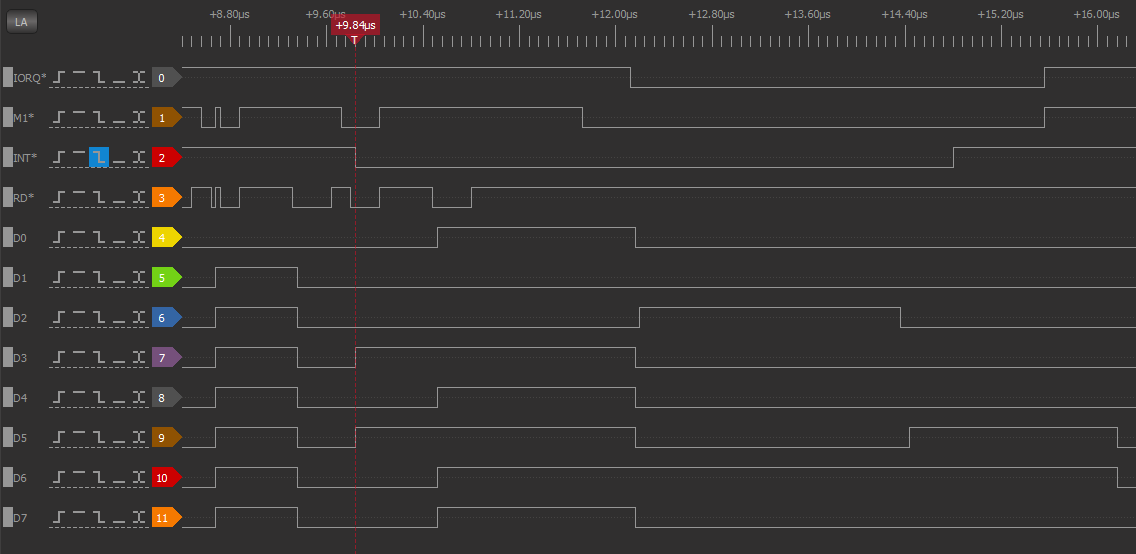

Interrupt Timing

The time from when an interrupt is created to when the interrupt is removed is about 5 uS.

I am using PSoC calls to functions that read/write registers. The inefficiency of the calls could be lessened by in access to the registers without calls. by When I tried putting the code in line I had trouble but it might be possible to figure out why. But it's possible that there were other things wrong with the code when I tried it

Writes to control registers could be posted and WAIT* removed more quickly. If the software is running a polling loop waiting on, say, transmit ready, it really doesn't matter much since the next serial write is waiting on the last character to be sent anyway.

Adding input and output software buffers and driving the interfaces with interrupts could also make the code faster. But, in the end it's just talking to slow serial interfaces.

land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.