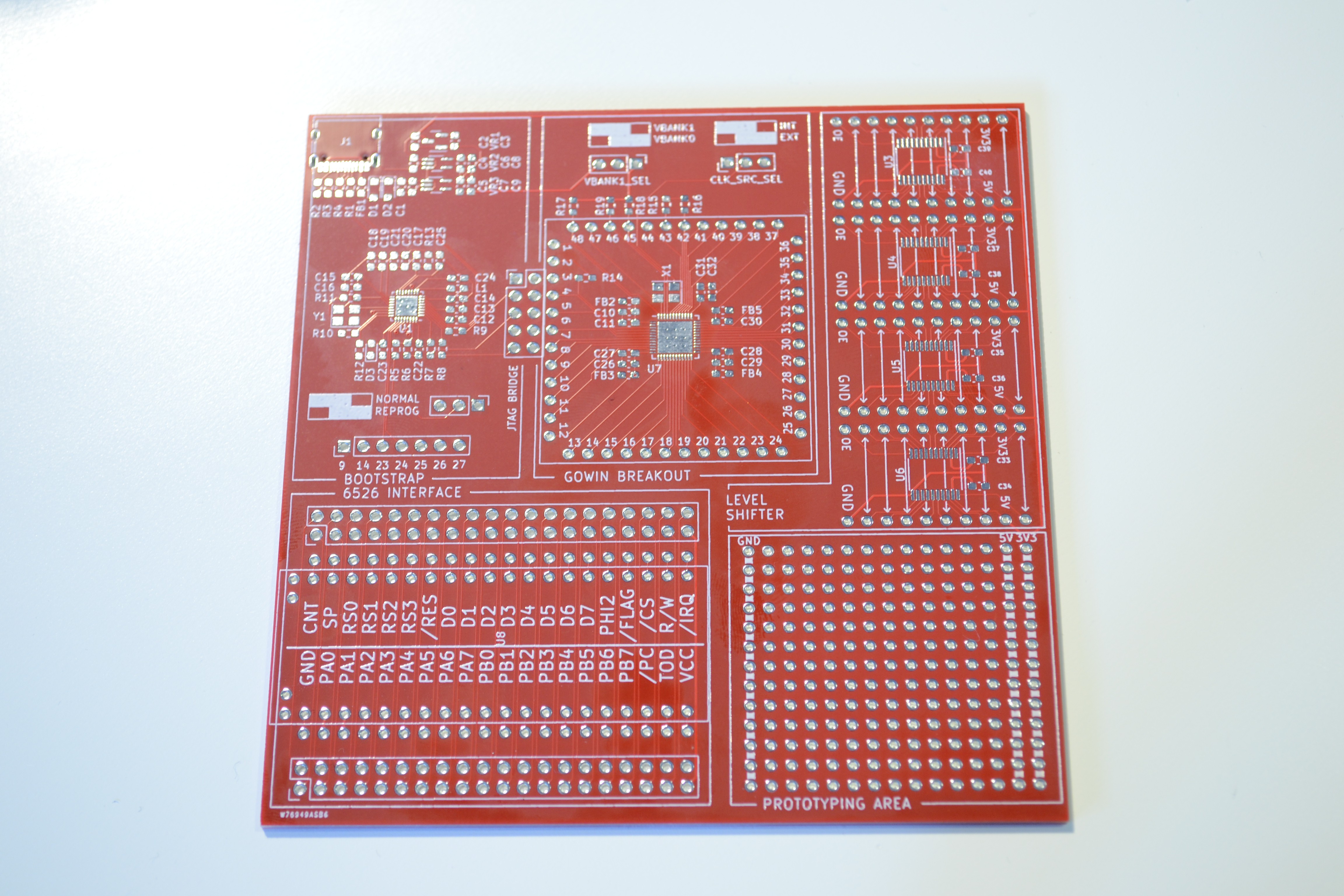

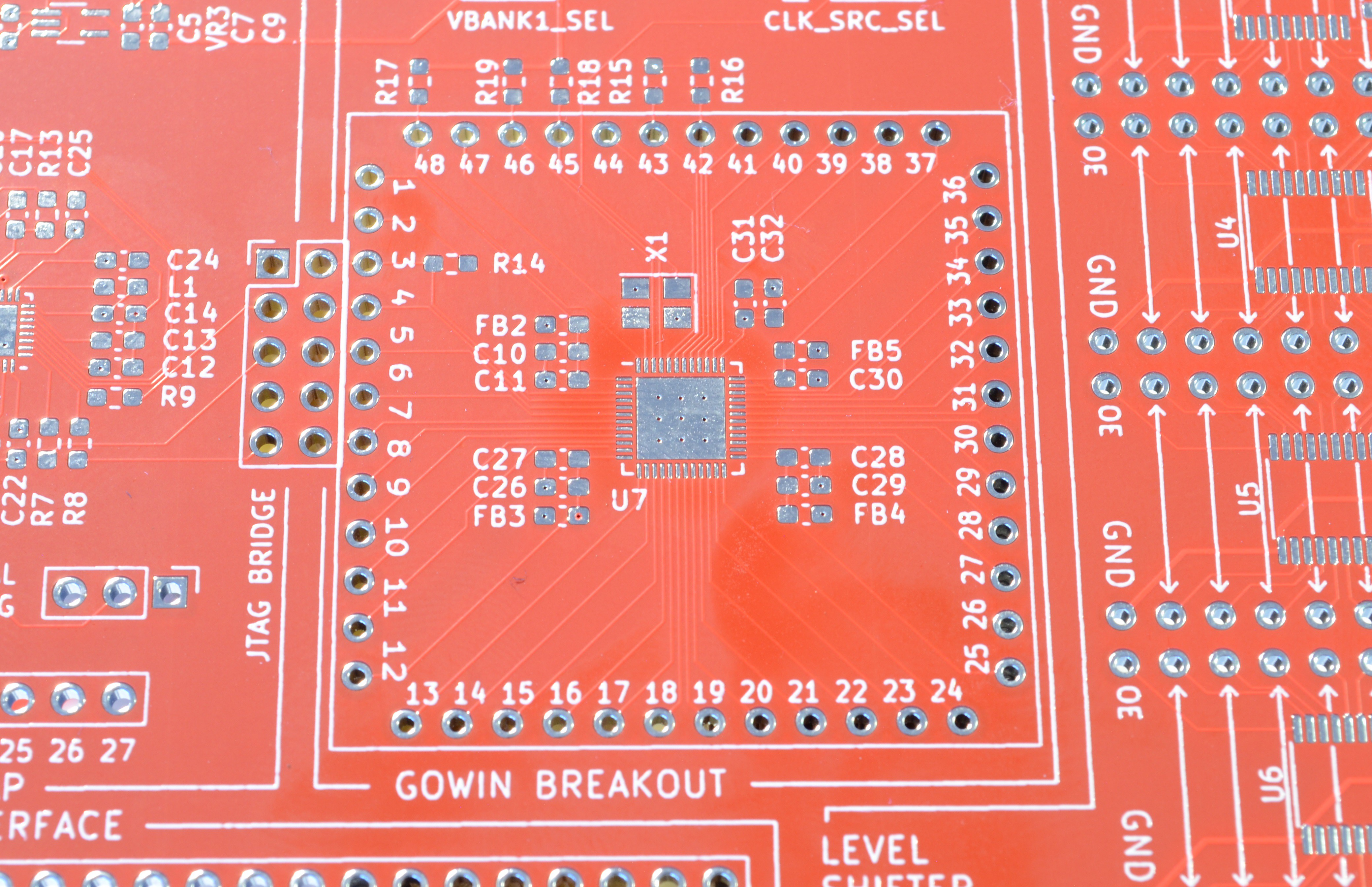

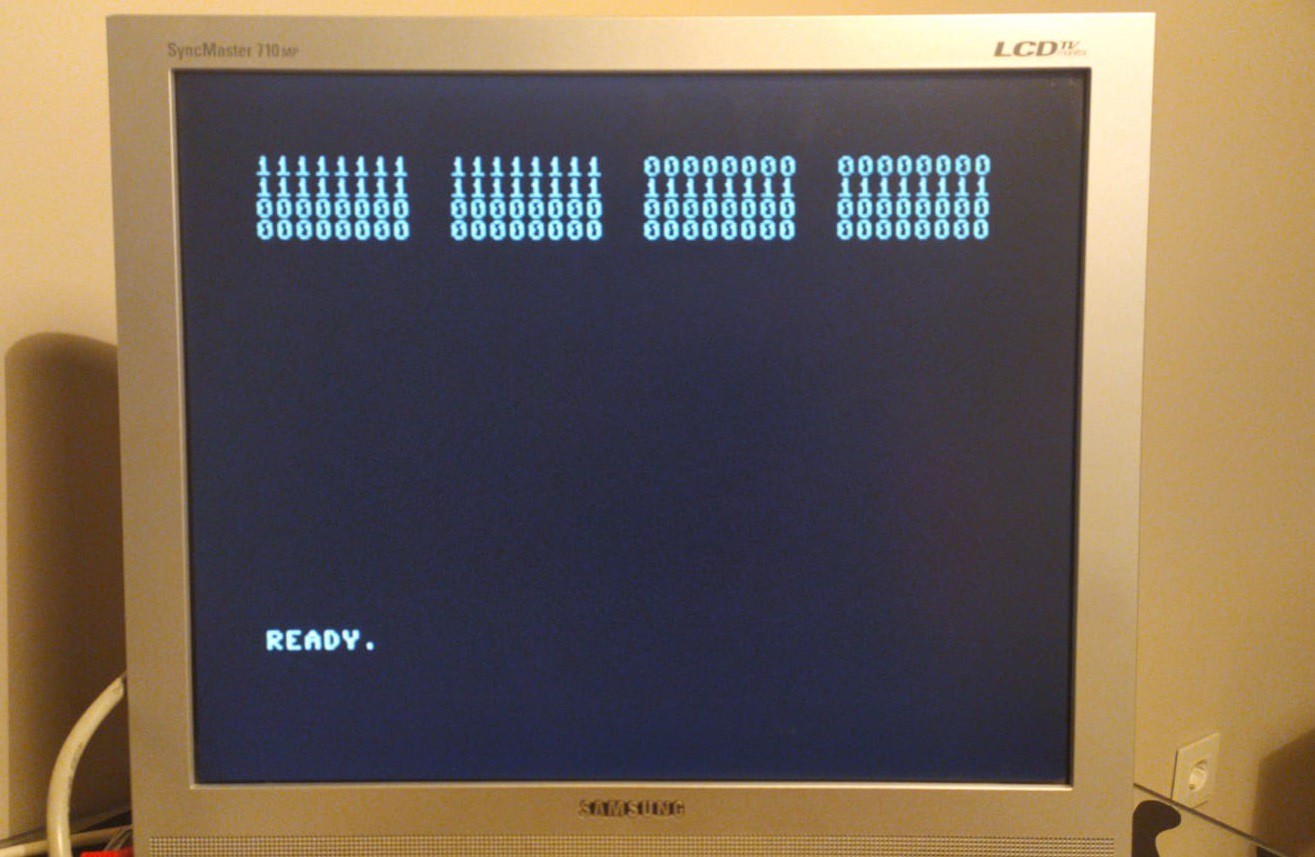

Inspired by the https://c74project.com/ the goal of this project is to build a drop-in replacement for the MOS6526, also know as CIA, used in many home computers by Commodore.

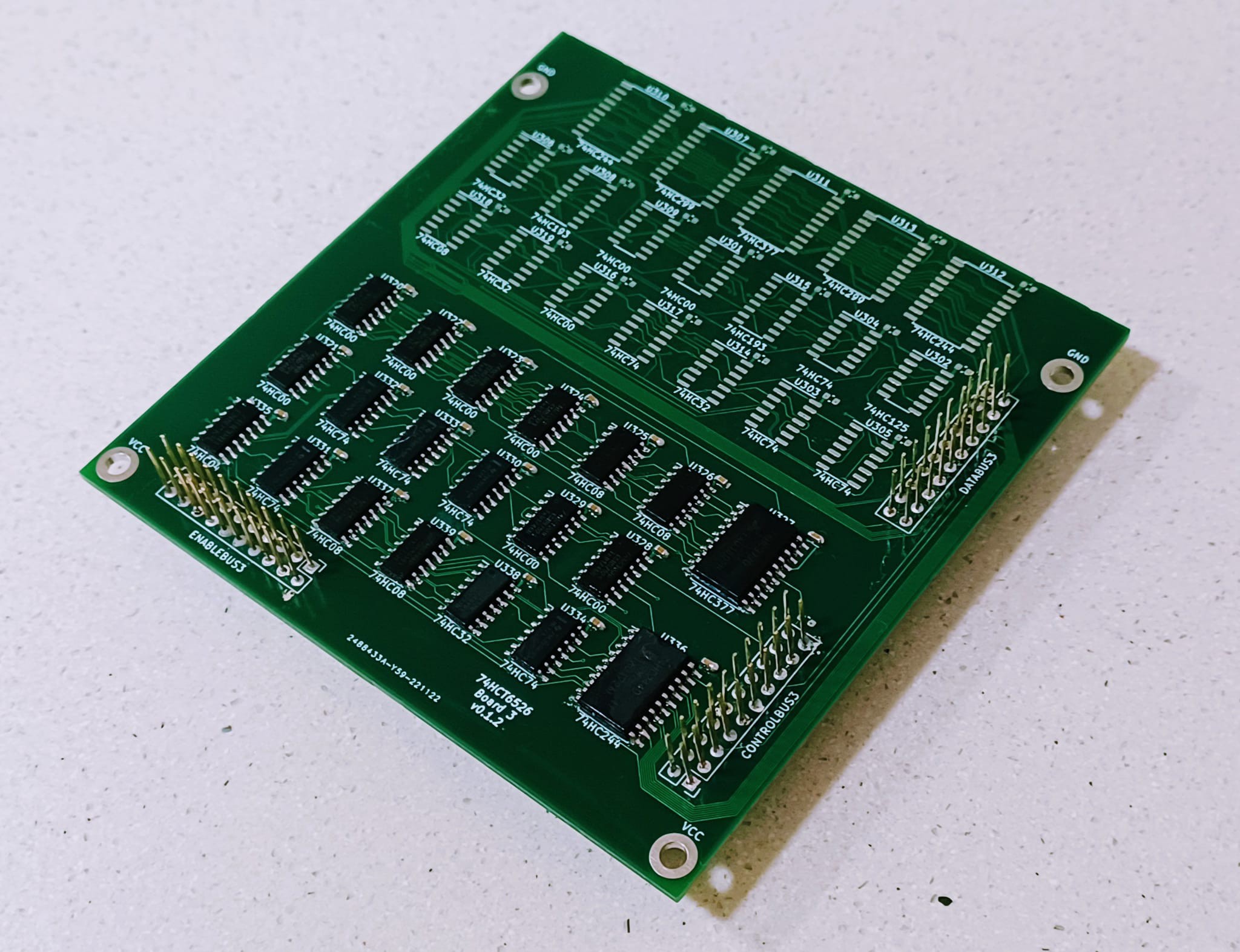

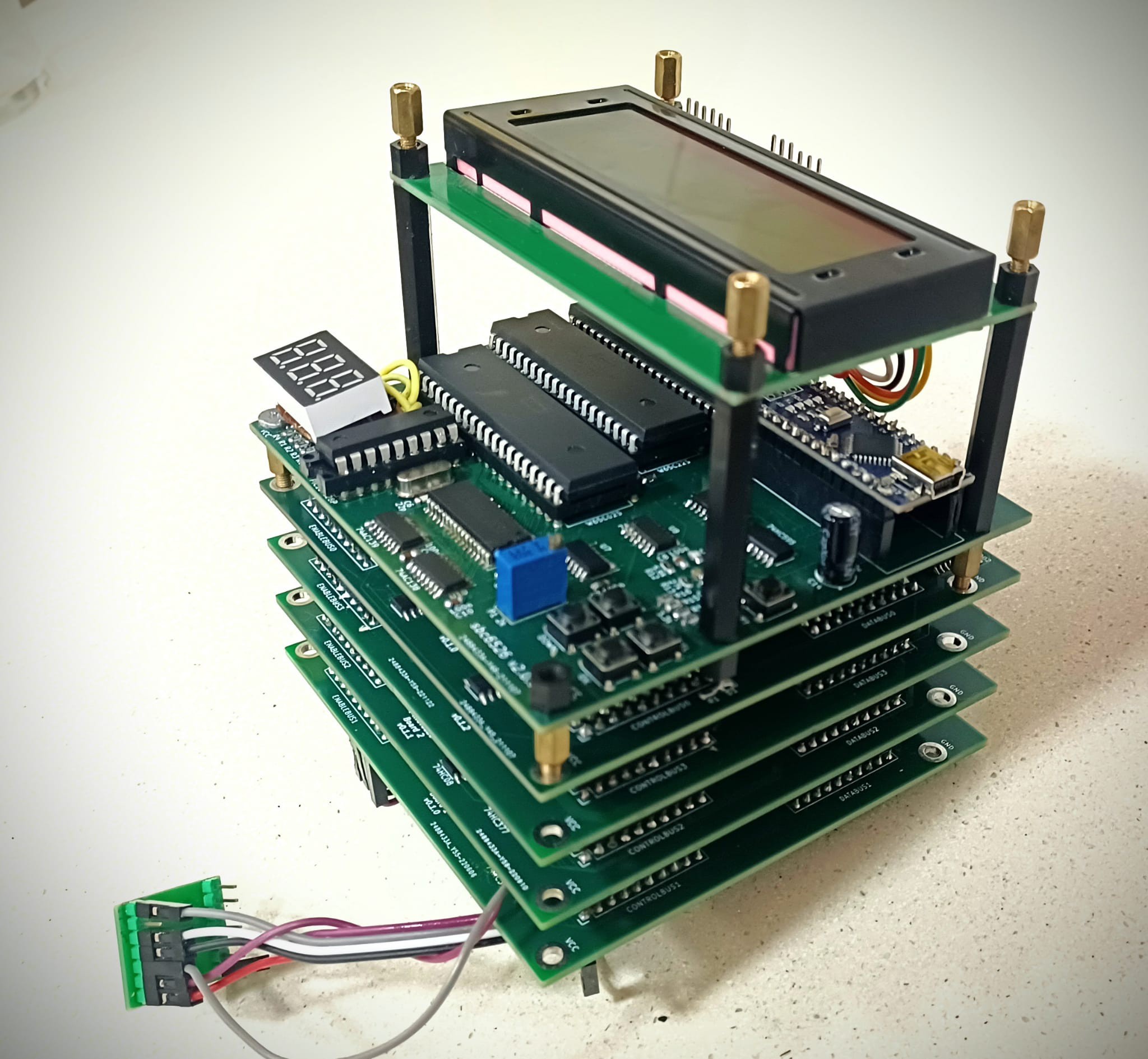

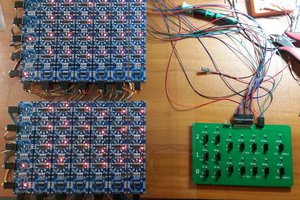

The final design aims to be build out of 5 boards:

- Board 0: DDR and PORT

- Board 1: Timer B

- Board 2: Timer A

- Board 3: TOD

- Board 4: SDR and ICR

Board 0 will also include the main computer interface, so it will include a connector to be attached to the computer itself.

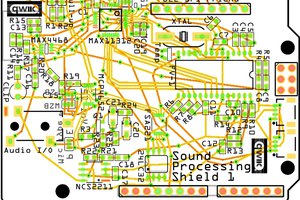

There are 3 vertical buses that will extend over the 5 boards carrying different control signals:

- ENABLEBUS: The 4-bit address selector is decoded into 16 individual enable signals, one for each register

- DATABUS: The 8-bit data bus from the computer, plus some other neccesary signals

- CONTROLBUS: Different control signals that are exchanged between registers

Dave's Dev Lab

Dave's Dev Lab

Ross Bamford

Ross Bamford

Matt

Matt

bobgreenwade

bobgreenwade

This is pretty cool. Looking forward to seeing the whole 5-board stack in action.