I'm currently at the stage of exploring this project in isolated parts, some of which I'm drawing in from my previous (unfinished) 68000 homebrew computer project.

I had originally planned for the 68000 computer to have 800x600 VGA output with 12-bit color (4 bits per channel), and a long time ago I had built a little prototype with an FPGA dev board and a resistor DAC. I only seem to have taken video of the 1-bit-per-channel variant:

However, after that I'd largely ignored the video part and shifted my focus to other details, such as the CPU itself, a basic emulator I could use to work on software when away from my bench, and very early iterations of a simple operating system.

I recently rediscovered that early video experiment and decided to iterate on its some more, with the intent of eventually including it in RISCoVite. This time I was a little more adventurous and decided to generate 720p HD video over DVI, after finding the TFP410 DVI encoder part that can convert from a parallel RGB signal to a DVI signal with very few supporting components and while allowing me to continue to run the FPGA logic at the relatively low clock speed that often befits a homebrew computer.

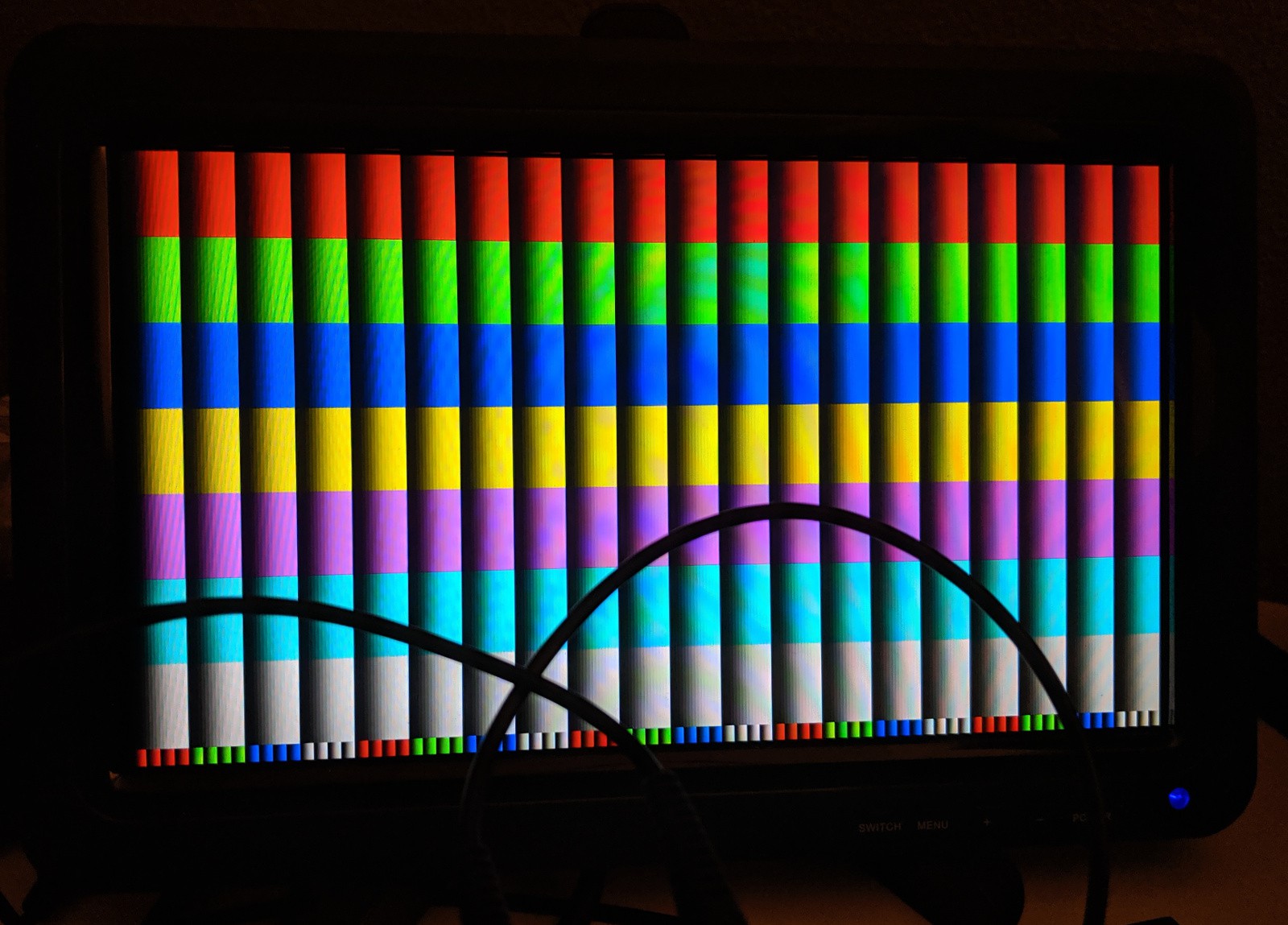

This time I settled just for a static test pattern rather than an animated demo, but did produce suitable output:

My camera and/or subsequent image scaling seemed to find some moire interference patterns in the image, but in "real life" the image is nice and crisp. Still 12 bits per channel, but now with fully digital signalling rather than a sloppy resistor DAC!

I've also been experimenting with rendering small "sprite" images from a block RAM, but so far the internal organization of the block RAM on ICE40 parts is still eluding me and I'm only managing a corrupt image that vaguely resembles the mouse cursor image I'm trying to produce as a test. I ran out of time for this round, but will have another attempt later.

I'm not sure yet if generating 720p HD output will actually be practical within the RAM limitations of the final design, because I'm planning for a bitmap-based display and at this resolution would need to dedicate about 1.3MB RAM just to the visible display, and I was hoping to also have enough video RAM left over for at least a back buffer to help keep things smooth on a system with a relatively slow CPU. We'll see! For now, I'm shifting my focus back to the CPU portion, wrapping a RISC-V core with a 68SEC000-like bus design so that I can continue to adapt portions of the former 68000 computer project.

I have more details on producing the above static test pattern in my personal blog article 720p Video from an FPGA.

Martin Atkins

Martin Atkins

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.