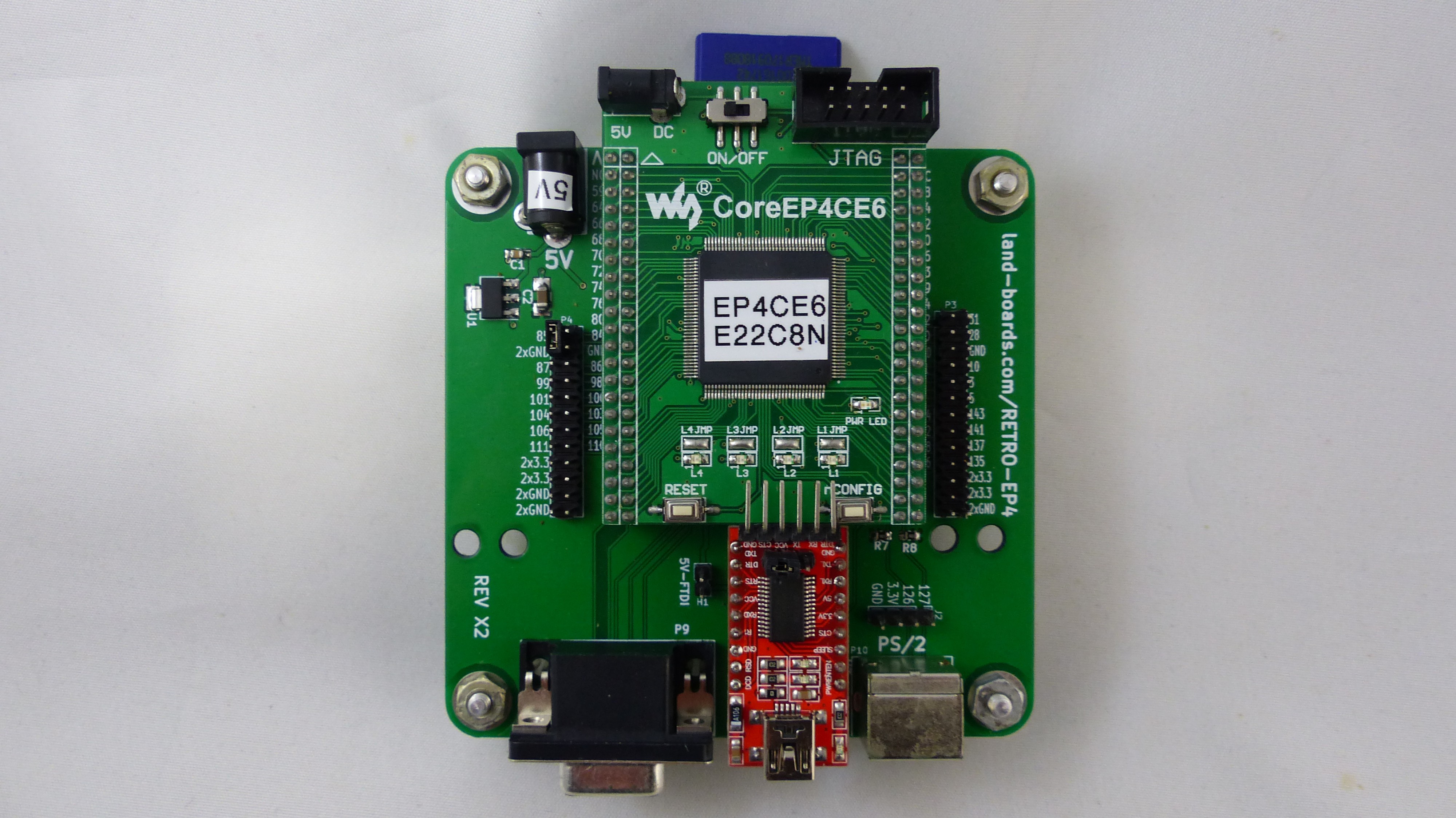

Ported the design to another FPGA card, the RETRO-EP4 card.

This card uses a smaller FPGA, the Altera/Intel EP4CE6. This FPGA has less resources than the EP4CE15 card. Both have more than enough logic cells to implement the CPU and other logic, but the EP4CE6 FPGA has less Block RAM. To make this fit the SRAM was reduced from 32KB to 16KB.

The features are:

- MC6800 CPU running MIKBUG from back in the day

- Hardware is RETRO-EP4 Card

- 16KB (internal) RAM version at 0x0000-0x3FFF

- 1KB (Internal) scratchpad RAM (512B used by MIKBUG) at 0xA000-0xA3FF

- MIKBUG ROM

- Select Jumper (FPGA Pin 135 on P4) switches between

- VDU (Video Display Unit) VGA + PS/2 keyboard (Open to GND)

- External Serial Port (Connected to GND)

Fit

+----------------------------------------------------------------------------------+ ; Fitter Summary ; +------------------------------------+---------------------------------------------+ ; Fitter Status ; Successful - Thu Mar 05 20:49:24 2020 ; ; Quartus Prime Version ; 18.1.0 Build 625 09/12/2018 SJ Lite Edition ; ; Revision Name ; M6800_MIKBUG ; ; Top-level Entity Name ; M6800_MIKBUG ; ; Family ; Cyclone IV E ; ; Device ; EP4CE6E22C8 ; ; Timing Models ; Final ; ; Total logic elements ; 2,940 / 6,272 ( 47 % ) ; ; Total combinational functions ; 2,827 / 6,272 ( 45 % ) ; ; Dedicated logic registers ; 802 / 6,272 ( 13 % ) ; ; Total registers ; 802 ; ; Total pins ; 47 / 92 ( 51 % ) ; ; Total virtual pins ; 0 ; ; Total memory bits ; 221,312 / 276,480 ( 80 % ) ; ; Embedded Multiplier 9-bit elements ; 0 / 30 ( 0 % ) ; ; Total PLLs ; 0 / 2 ( 0 % ) ; +------------------------------------+---------------------------------------------+

The Memory Blocks were:

; M9Ks ; 28 / 30 ( 93 % ) ; ; Total block memory bits ; 221,312 / 276,480 ( 80 % ) ; ; Total block memory implementation bits ; 258,048 / 276,480 ( 93 % ) ;

land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.