The four startup vectors for the 6800 are located near the end of memory space at $FFF8-$FFFF. The code contains an ORG to $C000 so there will need to be an EPROM that fills the entire 16KB space.

This size would be a challenge for the EP4CE15 FPGA since it would need 32KB for the SRAM and 16KB for the EPROM space for a total of 48KB. There's not enough blocks to do this in SRAM. There are several possible solutions to this challenge.

- The EPROM space is sparse and the EPROM could be emulated in logic since most of the values would return blank (filled with zero?). There are more than enough spare Logic Blocks in the EP4CE15 FPGA. This is done in Grant Searle's CEGMON EPROM as an example.

- The code ORG could be moved up in memory. This would present a challenge to code that relies on absolute addresses when calling the I/O routines built into the EEPROM but would work.

- The EPROM space could be replicated in the address space so that it appears in multiple places. This is done by messing with the address decodes. The 16KB could be eight copies of 2KB. This has the advantage of both being smaller (needing less memory blocks) and still provide the absolute addresses needed for I/O calls.

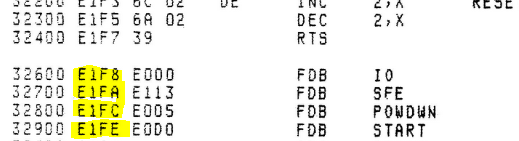

#3 seems like the easiest. This can be done by re-ORGing the base address of the vector table to the end of the EPROM space. The original MIKBUG was in a much smaller address space from $E000-$E1FF.

This looks like what MIKBUG is doing at the end of the code:

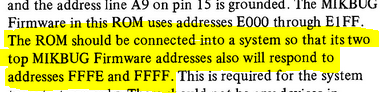

Here's the verbage from Engineering Note 100:

Here's the verbage from Engineering Note 100: Later note: Moved EPROM to $F000-$FFFF and opened I/O space from $FC00-FCFF so 60KB of SRAM can be used.

Later note: Moved EPROM to $F000-$FFFF and opened I/O space from $FC00-FCFF so 60KB of SRAM can be used. land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.