I was running the CPU at 12.5 MHz. Speeding up the CPU will requires some attention due to the external SRAM speed. The RETRO-EP4CE15 Card uses a 1MB 45 nS SRAM, the IS62WV10248EBLL-45TLI.

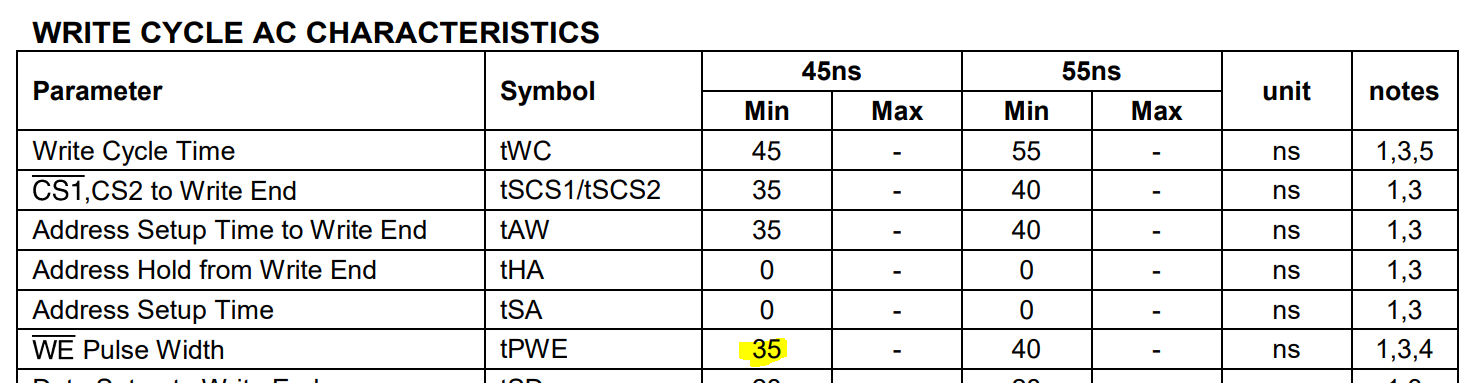

The critical timing is the write enable strobe:

The FPGA clock is 50 MHz or 20 nS per clock. Asserting the Write Enable (WE*) for 2 clocks works for the 45 nS parts that are used. 55 nS parts would be marginal but probably would work fine.

Write Enable should only be asserted while the CPU clock is high so it gets gated with the clock. Note, the logic shown here is inverted, eg, the signal goes high when the active low write enable is NOT asserted.

o_n_extSRamWE <= w_n_SRAMCE or w_R1W0 or (not w_vma) or (w_cpuClock);

This all says we can run the CPU clock at 16.67 Mhz with one 20 nS clock low and 2 clocks high.

The VHDL code for the CPU clock is:

-- ____________________________________________________________________________________

-- CPU Clock

-- Need 2 clocks high for externl SRAM can get by with 1 clock low

-- Produces a 40 nS wide wriye strobe - 45 nS SRAMs need a 35 nS write pulse, so this works

process (i_CLOCK_50)

begin

if rising_edge(i_CLOCK_50) then

if q_cpuClkCount < 2 then -- 50 MHz / 3 = 16.7

end if;

if q_cpuClkCount < 1 then -- 2 clocks high, one low

w_cpuClock <= '0';

else

w_cpuClock <= '1';

end if;

end if;

end process;

And it works!

25 MHz CPU Speed Upgrade

It could be possible to run faster by only stretching the CPU clock high width when the external SRAM is accessed. This way the CPU would run at 25 MHz when running from Internal SRAM and only drop to 16.7 Mhz for external SRAM accesses The change to the clock generator is fairly minor:

-- ____________________________________________________________________________________

-- CPU Clock

-- Need 2 clocks high for externl SRAM can get by with 1 clock low

-- Produces a 40 nS wide wriye strobe - 45 nS SRAMs need a 35 nS write pulse, so this works

process (i_CLOCK_50, w_n_SRAMCE)

begin

if rising_edge(i_CLOCK_50) then

if w_n_SRAMCE = '0' then

if q_cpuClkCount < 2 then -- 50 MHz / 3 = 16.7

q_cpuClkCount <= q_cpuClkCount + 1;

else

q_cpuClkCount <= (others=>'0');

end if;

else

if q_cpuClkCount < 1 then -- 50 MHz / 2 = 25

q_cpuClkCount <= q_cpuClkCount + 1;

else

q_cpuClkCount <= (others=>'0');

end if;

end if;

if q_cpuClkCount < 1 then -- 2 clocks high, one low

w_cpuClock <= '0';

else

w_cpuClock <= '1';

end if;

end if;

end process;

That worked, too!

land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.