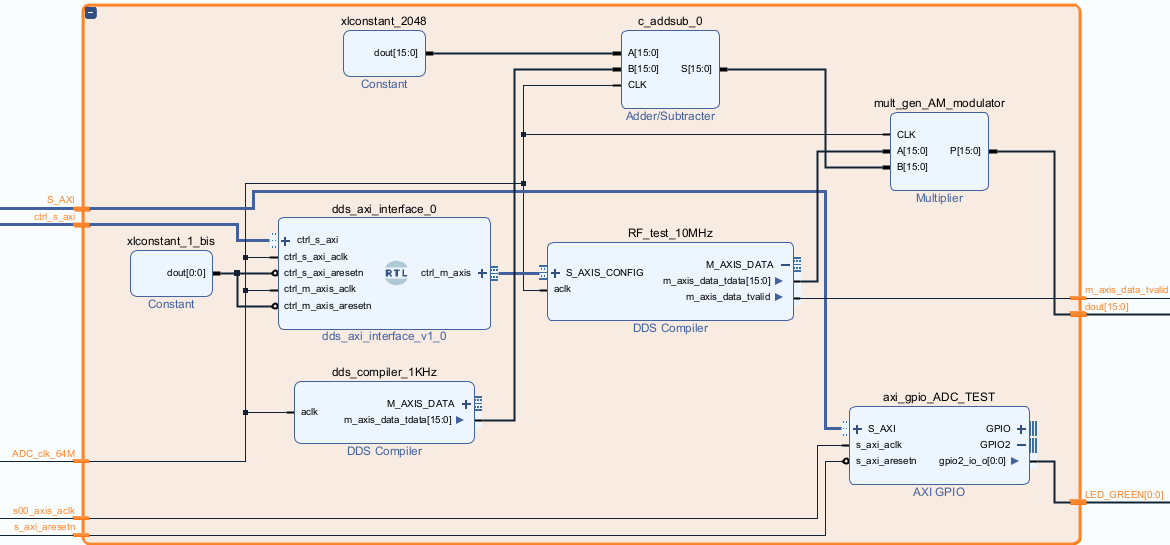

To test the fabric logic and the whole design even without an external signal and without involving the ADC, I rapidly understood the need of an internal test signal. Using a Xilinx DDS compiler IP I designed the following block:

The RF_test_10MHz generates a sinusoidal signal from 0.1MHz to 30MHz (default 10MHz) and programmable by dds_axi_interface_0.

The dds_compiler_1KHz generates a 1KHz 12 bits sinusoid (-2048 ... 2047) added to a 2048 constant value to obtain a 12 bits sinusoid between 0 and 4095.

The 1KHz sinusoid then multiplies (AM modulates) the test sinusoidal signal (e.g. at 10 MHz) obtaining the desired AM modulated signal roughly between -2048 and 2047 i.e. 12 bits after right shifting inside the multiplier.

Guido

Guido

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.