Jump Logic

The current jump logic uses JNC (Jump on Not Carry). It is a complete system but not that intuitive. For multi-nimble/byte arithmetic it is straight forward, if no carry adjustment is required (i.e. not carry), skip the add carry code.

A JGE (i.e. Jump on Greater or Equal) can be constructed by complementing one of the operands, and adding the other operand. Following is an example of testing the input for a program number 1 to 6:

Address OpCode Const Comment CODE # READ PORT 0 C F READ F 1 3 F LOAD M (PORT) 2 0 0 CLEAR CARRY # TEST PROGRAM 6 3 0 A ADD 10 # NOT 5 4 8 7 JNC 7 # JGE 5 5 E 7 SET PAGE # JUMP PROGRAM 6 6 8 0 JMP ADDR # TEST PROGRAM 5 7 0 1 ADD 1 # NOT 4 8 8 B JNC B # JGE 4 9 E 6 SET PAGE # JUMP PROGRAM 5 A 8 0 JMP ADDR # TEST PROGRAM 4 B 0 1 ADD 1 # NOT 3 C 8 F JNC F # JGE 3 D E 5 SET PAGE # JUMP PROGRAM 4 E 8 0 JMP ADDR # SET NEW PAGE 1 F E 1 PAGE 1 # TEST PROGRAM 3 10 0 1 ADD 1 # NOT 2 11 8 4 JNC 4 # JGE 2 12 E 4 SET PAGE # JUMP PROGRAM 3 13 8 0 JMP ADDR # TEST PROGRAM 2 14 0 1 ADD 1 # NOT 1 15 8 8 JNC 8 # JGE 1 16 E 3 SET PAGE # JUMP PROGRAM 2 17 8 0 JMP ADDR # TEST PROGRAM 1 18 0 1 ADD 1 # NOT 0 19 8 C JNC C # JGE 0 1A E 2 PAGE 2 # JUMP PROGRAM 1 1B 8 0 ADDR 0 # RETURN - NO PROGRAM SELECTED 1C E 0 SET PAGE 0 1D 8 0 JMP ADDR 0 1E 0 0 NOP 1F 0 0 NOP

One option is to add a comparator to the ALU and to use one of the flags (i.e. A<B, A=B and A>B) or the compliment to trigger the jump. It would have the advantage of not altering the accummulator.

---

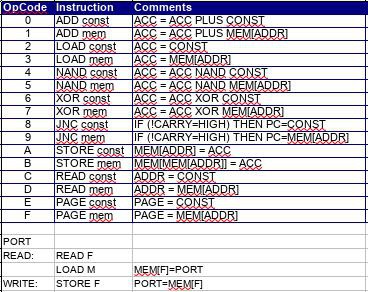

I have been thinking more about this. It would be an efficient and useful to have a "TEST" register but it requires freeing up an op code. XOR being the one to use:

But rather than doing that I am thinking of an op code to select an alternate op code set.

PAGE and READ are similar so they could share the same op code, and the PAGE slot used to set alternate op codes:

- ADC/SBB

- LOAD/LOAD

- NAND/NOR

- XOR/XOR?

- JNC/JGE?

- STORE/STORE?

- READ/PAGE

- OPCODE?/OPCODE?

Another option is to use the most significant bit of the PAGE register.

ADC/SBB, the ADC requires an inverter on the input and on the output for SBB (have to check this). Does JNC become JNB which is JGE? No need for a dedicated comparator?

AlanX

agp.cooper

agp.cooper

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.