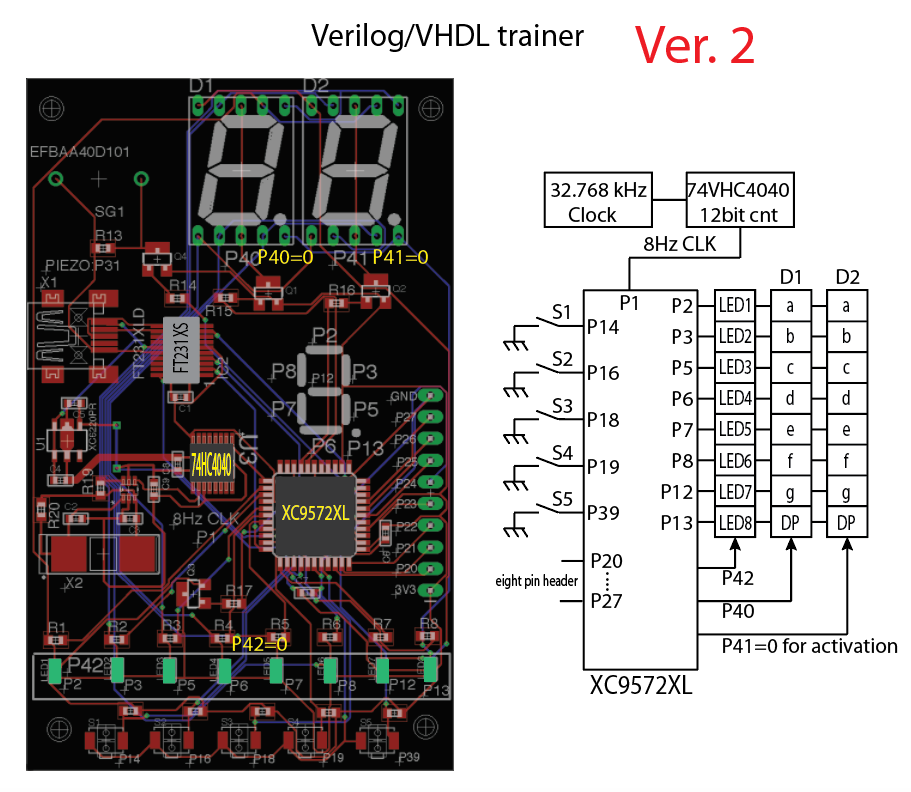

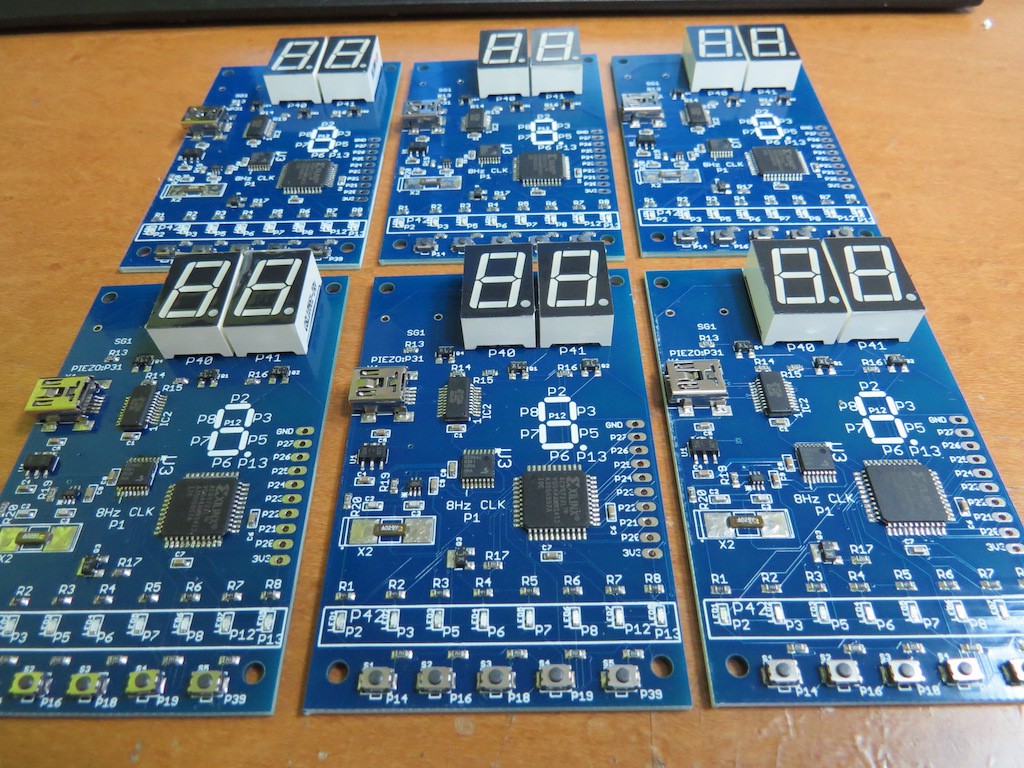

Now the rev.2 of VHDL/Verilong training board is done!

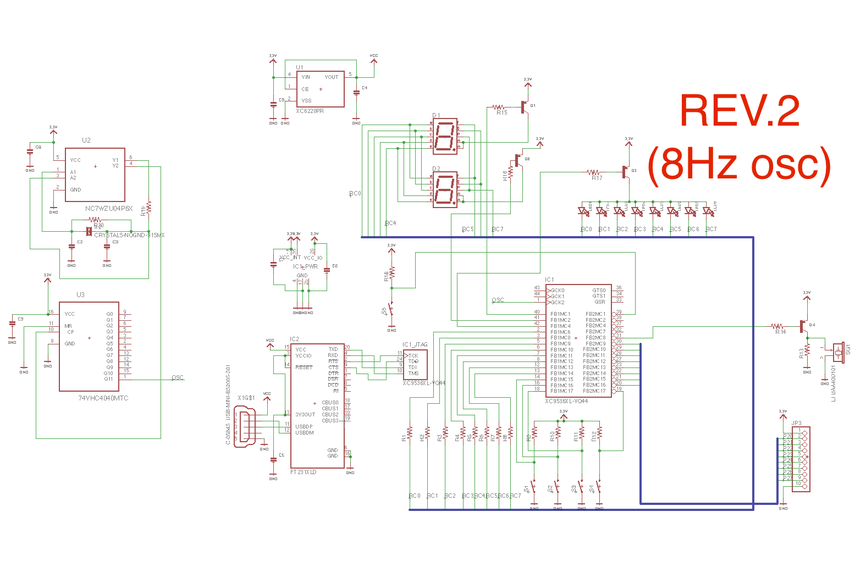

Basically the same circuit but now it's 3.3V operation with XC9572XL (72 macro-cells), which is double sized to the previous one. In addition, 8 Hz (not 8 kHz, also not 8 MHz) clock generator provided by 32768/4096 is on board. For real starting point of hardware description language study, this type of very slow clock is very useful for fundamental confirmation. Tactile switch and LEDs are switched to SMT type for smaller footprint.

As you would see, empty area can be found. This space is prepared for Piezoelectric speaker for sound application it is totally useless for 8-Hz operation (too low for audio signal generation) so the piezoelectric speaker is NOT populated. The circuit is connected to P31 of XC9572XL and if 32768Hz crystal will be swapped with higher frequency , for example 16MHz crystal, we will hear 3.9kHz sound for proper implementation. Please add speaker for such cases by yourself. (or taking another tap of 74VHC4040 will also work..)

How to use this board by ISE

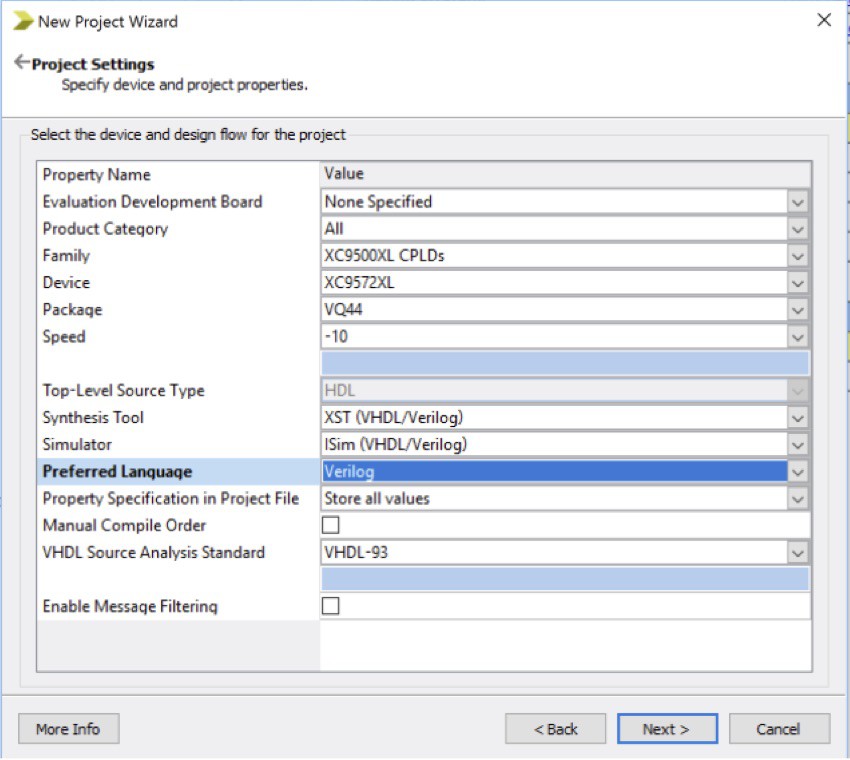

As same as previous version, XC9500XL series also not supported by up-to-date Xilinx Vivado but perfectly works with Xilinx ISE. Setting is almost same as previous one and I would show here only for the different part.

In the project setting, please select XC9572XL/VQ44 speed -10 version. Other part of setting are exactly the same as previous XC9536/5V version. please refer my previous log

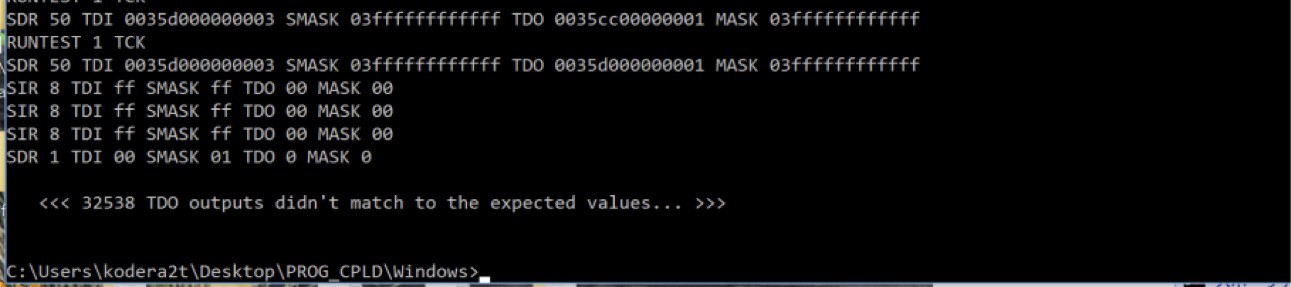

In some case, we will see this kind of error message. (once board is well recognized by your computer, we will seldom meet this situation..)

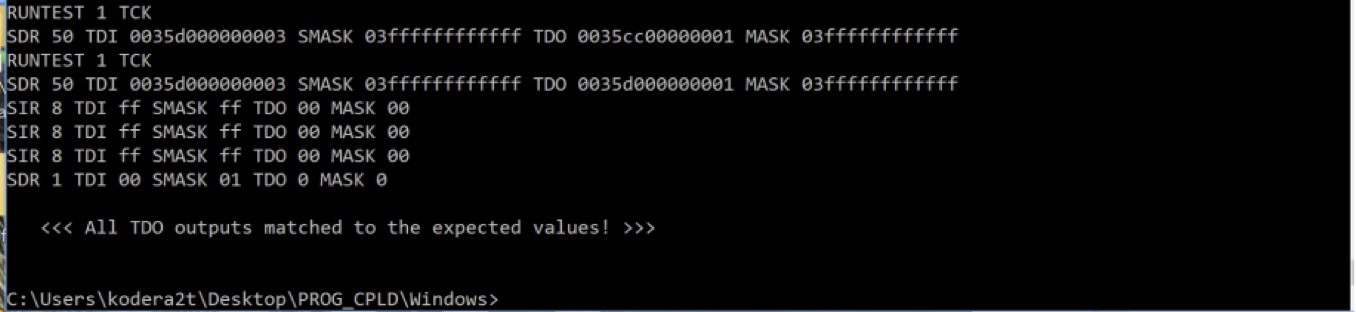

This is saying "32538 TDO didn't match" meaning writing is not succeeded. In such a case, please do not throw the board to trash but just simply, plug-off USB and plug-in USB again, and write the same .svf file again. Just repeating again,,

You will see "No error" message. As same as previous board, after writing new .svf file, we need to restart CPLD by plug-off-in process.

The circuit is not so complicated and you would try to make by yourself but also this board is available at my tindie store!

kodera2t

kodera2t

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.