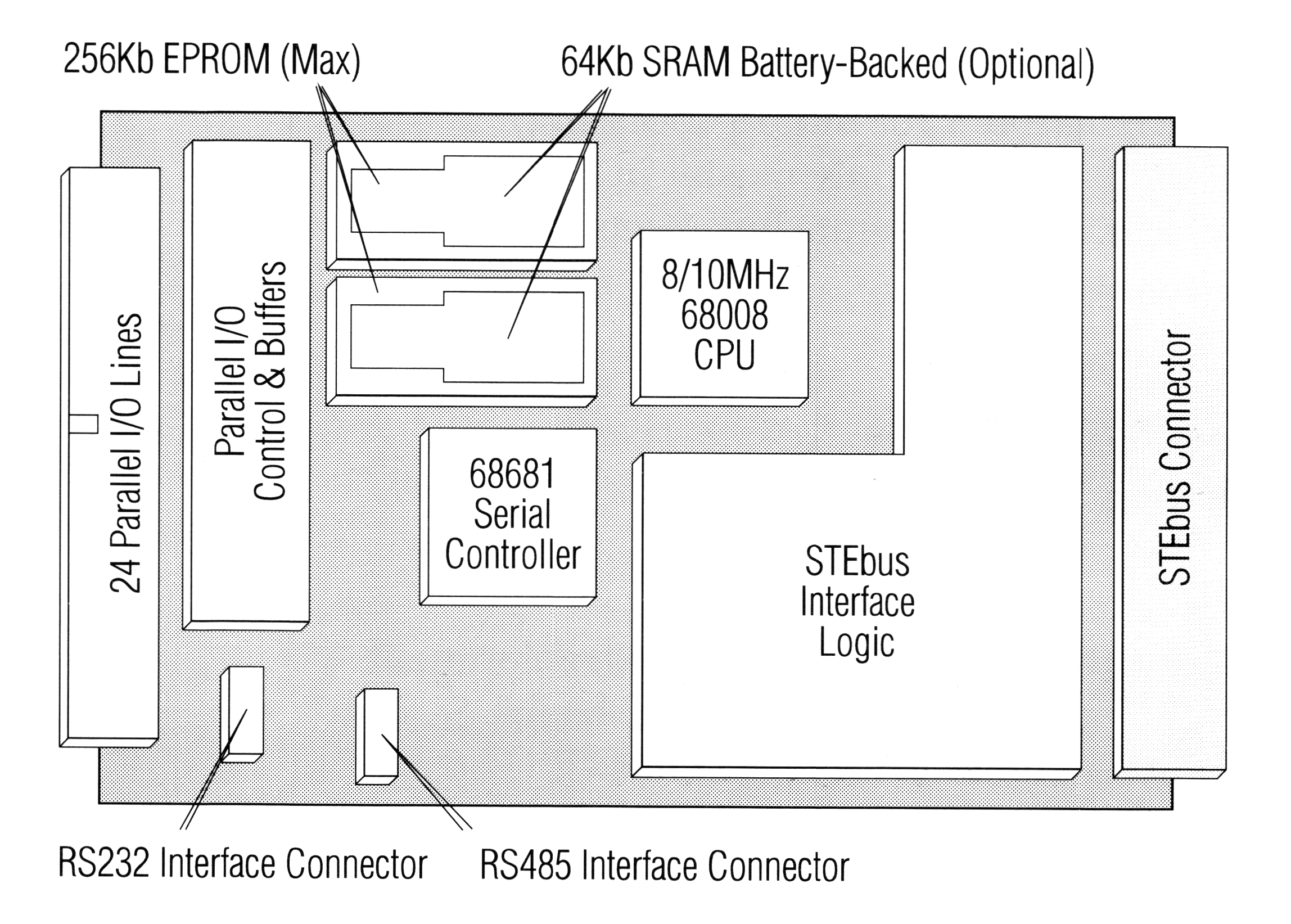

The SC008PIO is a based on a 8 MHz 68008 processor (optionally 10 MHz), and is designed as a target-orientated processor for standalone operation, or as the main CPU in larger systems.

The board has sockets for up to 256Kbytes EPROM and up to 64Kbytes of Static RAM. The SC008PIO also integrates 24 buffered parallel I/O lines on a 50-way connector with the industry standard Signal Conditioning Bus pin-out. Eight lines are output (24mA sink), eight lines are input, and eight are bit- bidirectional (with 16mA sink capacity). This means that low-cost target systems can be built with just the SC008PIO and a Signal- Conditioning board. Another feature is the ability to battery back-up the on-board 64Kbytes of the Static RAM, using an off-board battery (not supplied).

A 68681 provides two RS232 asynchronous serial ports and a counter/timer. One of the serial ports may be configured to the on-board RS485 transceiver for multi-drop networking. The counter/timer provides the clock for real-time operating systems.

Exactly the same code and development tools can be used as on the SC008, since the SC008PIO is an enhancement of the SC008. Software available includes the powerful OS-9/68K multi-tasking/multi-user, ROMable operating system.

Interface:

STEbus default master interface.

Power consumption:

1.3A @ 5V, 30mA @ +12V

Features:

- 8 or 10MHz 68008 processor

- 24 parallel I/O lines

- 64Kb battery-backed SRAM capability

- Up to 256Kb EPROM

- Compatible with SC008 software

- Two RS232 serial ports

- One serial port configurable to RS485

- Accepts and generates bus interrupts

Ordering Information:

SC008PIO 8MHz 68008 CPU, with 64Kb SRAM SC008PIO10 10MHz 68008 CPU, with 64Kb SRAM

Development Systems

The ARC008PIO-35 is a STEbus OS-9 development system based on the 8MHz SC008PIO CPU board. System construction is as for all STEbus CPU board development systems, and includes:

- 8MHz 68008 CPU

- 512Kb DRAM

- Real-time clock

- Floppy Disk Controller

- 40Mb hard disk (SCSI)

- OS-9 Professional Operating System

- SC008PIO

- SDRAMD

- SCRAM

- SFDC

- SCSI

- SBPLM14

- PSU17TC

- OS-9 Professional

Block diagram

Keith

Keith

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.