Answer: less than 500ps Tpd, sometimes. I built a gated ring oscillator with some single-gate 74AUC packages just to see how fast it would run. The 74AUC family seems to offer the fastest CMOS gates you can buy at at moment, guaranteeing a 1.6 ns max propagation delay at 2.5V. It looks like they can be significantly faster in practice, especially if you crank up the voltage a little :-)

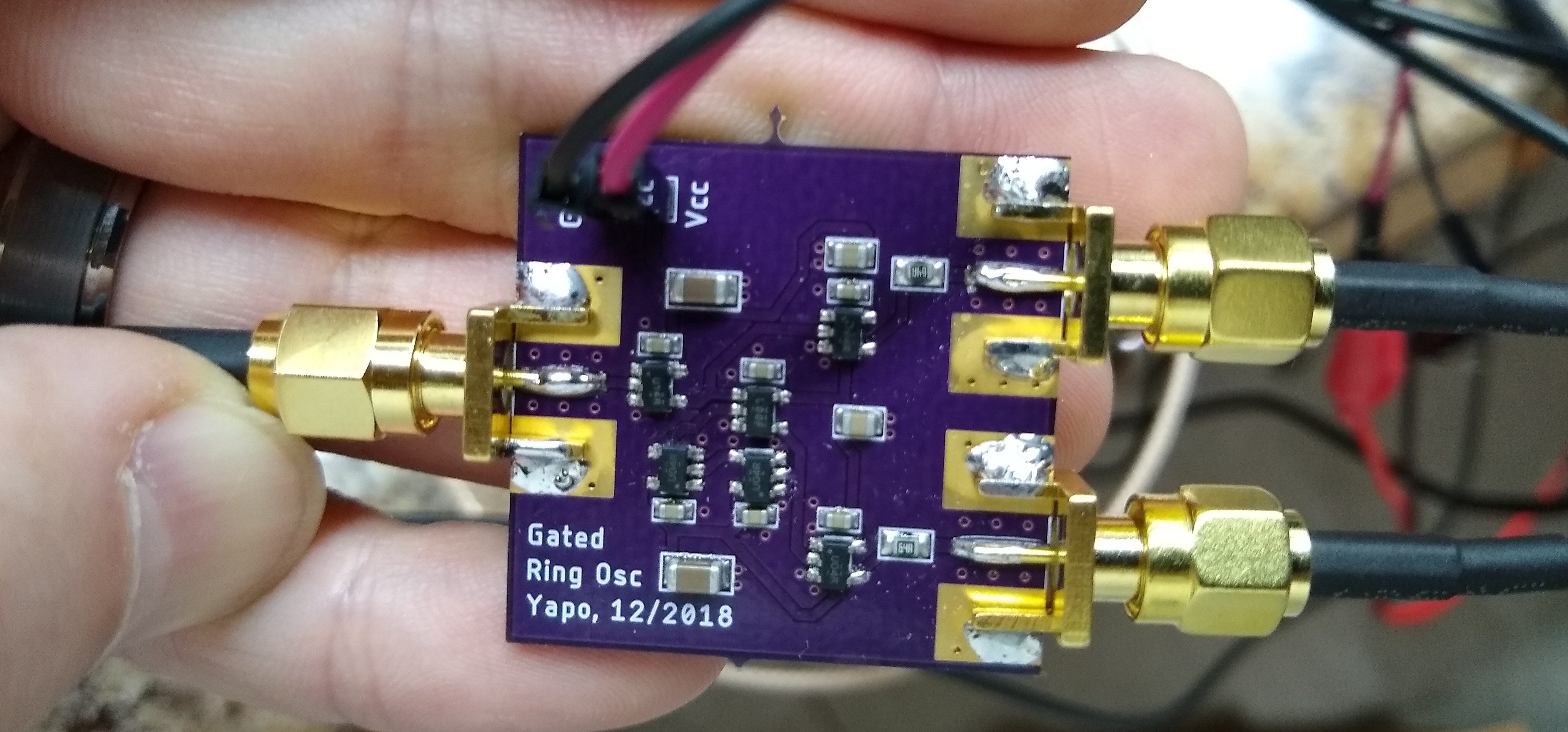

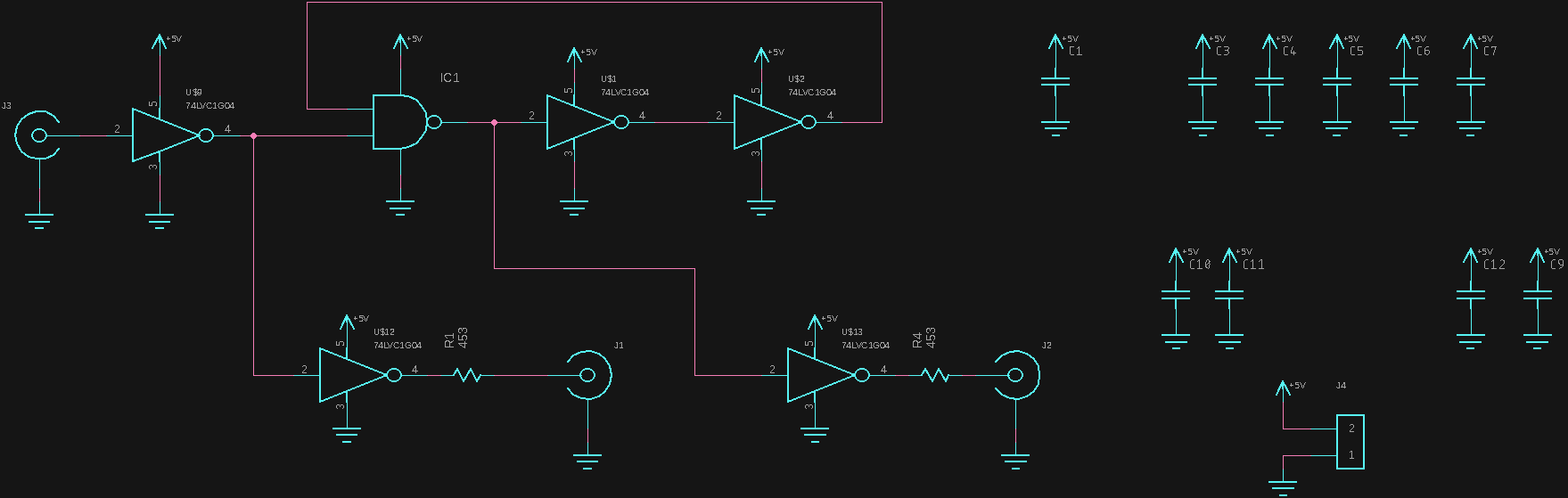

The circuit is very straightforward. A 74AUC14 Schmitt-trigger inverter buffers the incoming gate signal. The output of this buffer gates the oscillator through a 74AUC00 NAND date and also drives a 74AUC04 for an output driver. The ring oscillator itself consists of two additional 74AUC04 inverters plus the NAND gate. Finally, one more 74AUC04 inverter is used as a driver to buffer the output. 453-ohm resistors are used at the outputs to create 10x dividers when combined with 50-ohm terminated oscilloscope inputs. The 74AUC gates are plenty fast, but don't source/sink enough current to drive 50-ohm cables directly, necessitating the use of these 10x "probes."

I'm running them at 3.3V, which is within their absolute max voltage of 3.6V, although the datasheet says they're recommended for up to 2.7V, and optimized for 1.65-1.95V supplies.

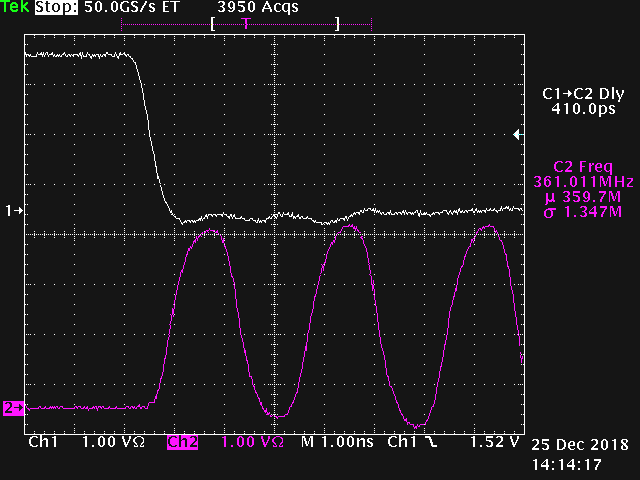

So, how fast are they? The oscillations start 410ps after the gate signal edge and run at 360 MHz. This frequency implies a mean propagation delay for the inverters and the NAND gate of 463 ps. That's very fast for gates you can essentially treat like your normal CMOS friends (except, of course for the fast edge rates, discussed below).

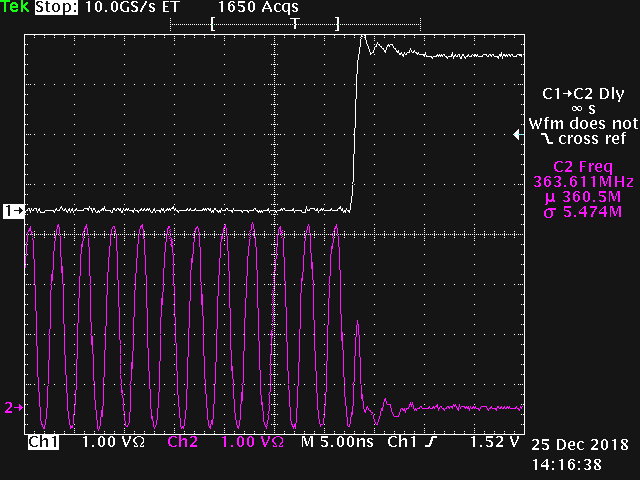

While the oscillator startup time of 410 ps is impressive, this circuit generates runt pulses at the end of the gate interval, unless the gate time happens to be an even number of cycles of 360 MHz. You can see a runt pulse generated at the rising edge here:

If this oscillator were driving a counter, that last pulse might or might not be counted. And, of course, the actual oscillation frequency will vary with voltage, temperature, and individual parts. Actually using this thing would be a non-trivial exercise in calibration.

I'm impressed with the 74AUC gates. When I built a similar circuit with 74AC gates, which I used to consider "fast," I measured a startup delay of 2.5 ns and frequency of 76 MHz. This circuit starts up 6 times faster and oscillates almost five times as fast. I think the only way to go faster is to switch to ECL parts, which I might as well try since I've gone this far.

While I had the circuit on the scope, I took a look at the edge rates from the 74AUC04's. The rise time was 560 ps and fall time 528 ps. This is not much faster than the 74AC gates which I measured at 700 ps and 650 ps, respectively. This may be part of the reason the 74AC series had such a reputation for bad behavior - the sharp edges manifest transmission-line effects on relatively short traces, even though the clock rates may not be that high. The 74AUC gates, on the other hand, actually seem to show propagation delays shorter than their edge rates, which is impressive - but I'm not convinced this is the case yet. I'm waiting on a few adapters so I can connect these outputs directly to the scope without using cables. At these speeds, dispersion in the cables might be affecting the edge rate measurements.

EDIT 20181226

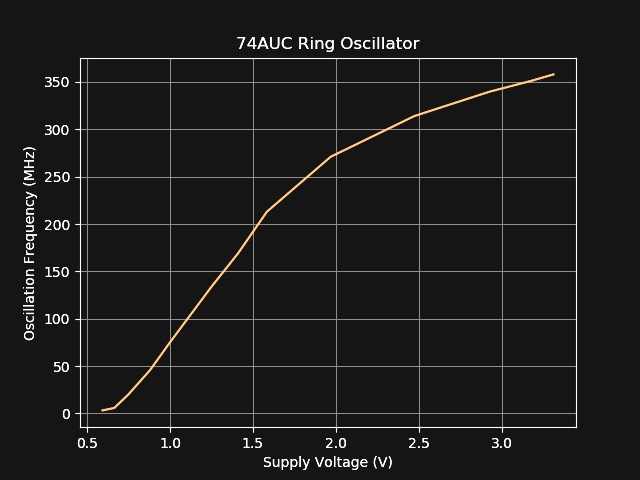

@Yann Guidon / YGDES asked about frequency vs supply voltage. Here it is:

The datasheet says 0.8-2.7V, but it worked down to 0.6 and a little below in my tests. You could probably make a half-decent PLL with this thing, especially below 200 MHz.

Ted Yapo

Ted Yapo

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

I just reviewed Texas Instruments data sheets for several SN74AUC1G gates. It seems that perhaps you could shave some more time in the ring, increasing oscillators frequency, by substituting two inverters for one non-inverting gate, e.g. a 74AUC1G32.

Are you sure? yes | no

That might work. If so, maybe a 74AUC1G32 plus a single inverter might also work.

Are you sure? yes | no

it might :-D

but what matters is individual gate latency ;-)

Are you sure? yes | no

So how do these compare to the Potato "GHz" -range of devices in a real world application where the connected gates input capacitances bogs everything down to like half speed?

Are you sure? yes | no

I have never seen any of the fabled Potato chips...now that makes me want to track down one of the beasts and see what it can do.

I think the use case for single-gate packages probably doesn't include the capacitance-limited large fan-outs you're describing. They probably get used where the designer needs one to a handful of gates but doesn't have programmable logic resources available. In that case, if you need the speed, you keep fan-outs low (1), and keep the point-to-point tracks a constant impedance.

OTOH, you probably can come up with a case where the 74LVC family with it's slower Tpd but larger current drive (32 mA vs 8 mA for the 'AUC) can drive large fan-outs faster.

Are you sure? yes | no

Oh, I read the datasheet for one of the Potato chips and see what you mean. The advertised Tpd uses a smaller loading capacitance than one of the chips's own inputs. I bought two on ebay to try them out anyway.

The 74AUC's seem to be able to drive themselves at rated speed :-)

Are you sure? yes | no

Yes, the potatoes are cool but at the same time really silly. I wonder if there's anything that they can be connected to without compromising the speed except an active oscilloscope probe that usually have less than 1 pf capacitance. ;-)

But any real world application with them would require one or more inputs and capacitances agents the power planes on the pcb.

Well, it will be interesting to see what you can come up with using them.

Are you sure? yes | no

I'm waiting for your next measurement : a curve of osc. frequency vs Vcc :-)

Are you sure? yes | no

Done! See above :-)

Are you sure? yes | no

YAY ! Great job ! (as usual)

Are you sure? yes | no

"That is some pretty interesting information" :-)

almost 10 years ago, I imagined building a small processor only with single-gate chips, "just for the fun". It would not be that slow, after all...

Are you sure? yes | no

It would probably be very fast! There's some *really* interesting info in the TI app note for 74AUC. The output drivers dynamically change their impedance during transitions, and they've designed the curve to minimize rise/fall time, but then assume around 50-65 ohm impedance to absorb reflections. The result is that you can supposedly drive 50-ohm traces on a PCB without adding termination resistors - they claim up to 15 cm. That would make routing your little computer much easier :-)

http://www.tij.co.jp/jp/lit/an/scea027a/scea027a.pdf

Are you sure? yes | no

"You had my curiosity, now you have my attention".

Are you sure? yes | no

https://i.imgur.com/uu9pmDP.gif

Are you sure? yes | no

That's the biggest issue with the LVC. The fast rise/fall time requires series termination for anything longer than 1/2" of tracks. Your tiny logic is no longer tiny because of that.

I had a run in with this issue on a Silabs eval board on the external program connector as they didn't have terminations. The connection were so unreliable until I added resistors.

Are you sure? yes | no

What you are saying is that the half nanosecond gate delays of the dark magic ECL circuits of my youth are now matched by inexpensive sane logic level CMOS. And they will have switch rate proportional power usage. Cool.

Are you sure? yes | no

I think that's the long and short of it. They're pretty nifty little gates.

Then again, ECL hasn't stood still all this time. 100EP gates advertise 220 ps Tpd, with listed minimums of 160 ps, so they should go 2-3x as fast. But the expense and crazy levels remain.

Are you sure? yes | no