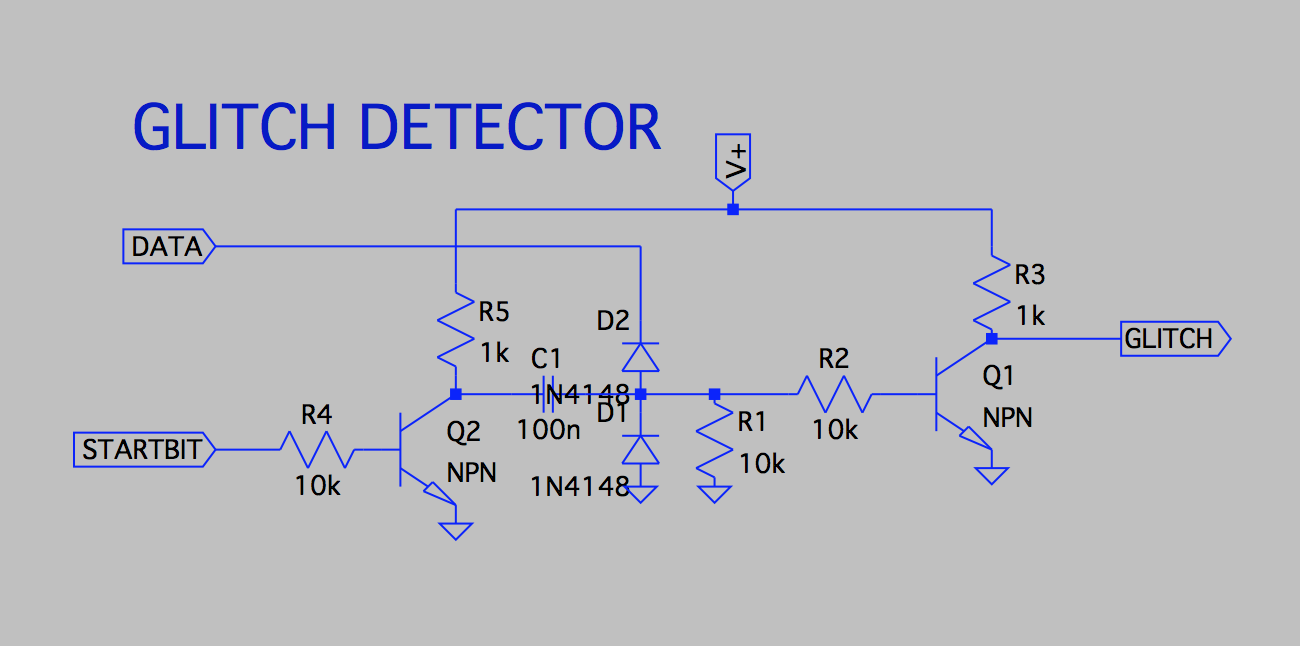

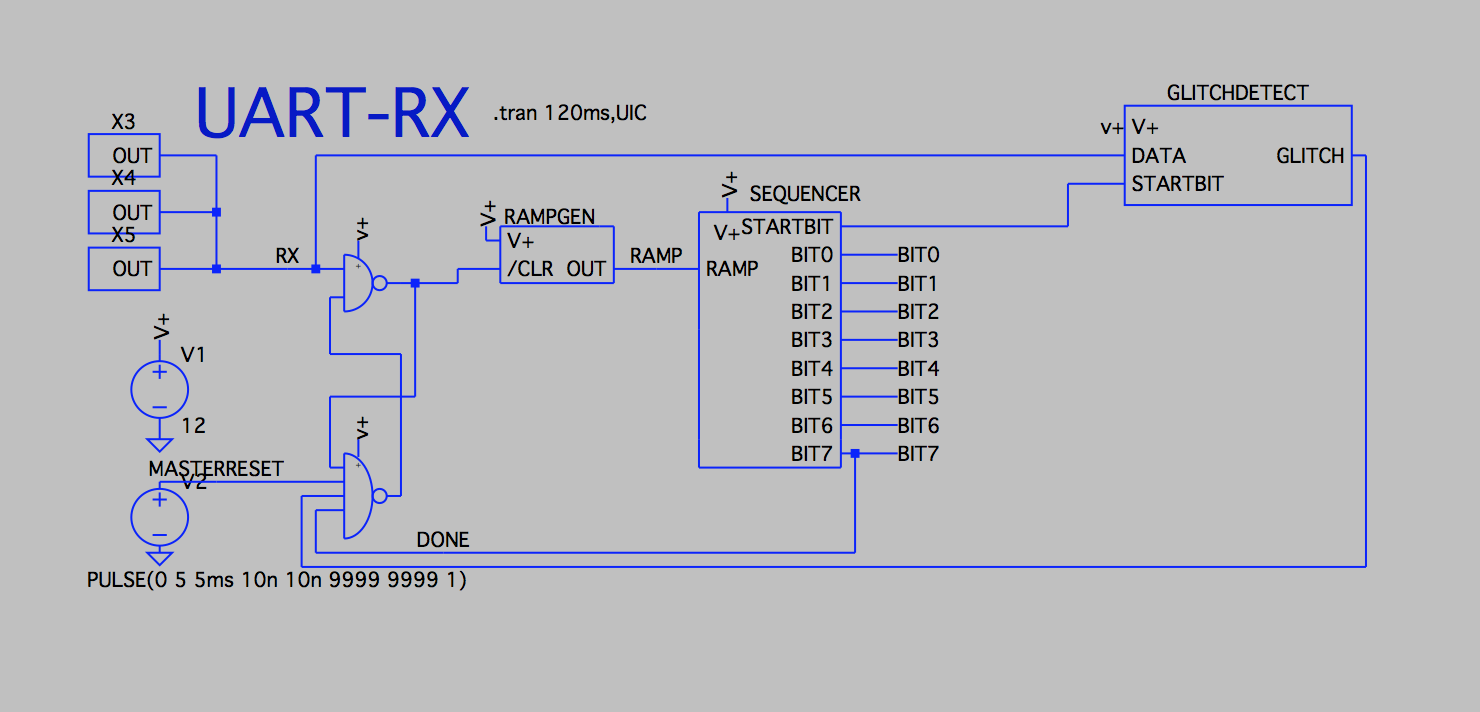

Most "real" UARTS have a glitch detector that detects false startbits. I added a simple glitch detector that verifies that the startbit is still active in the middle of the startbit time slot. If the line has returned to idle again then the receiving sequence is aborted.

For this I had to increase the 3-input NAND in the start/stop logic to a 4-input NAND. That was not too much of a hassle, just added one diode :-)

I also added two more TX-fakers to simulate one additional character arriving on the line to see if the design handles more than one character (it does), and also simulate a glitch to test the glitch detector.

matseng

matseng

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.