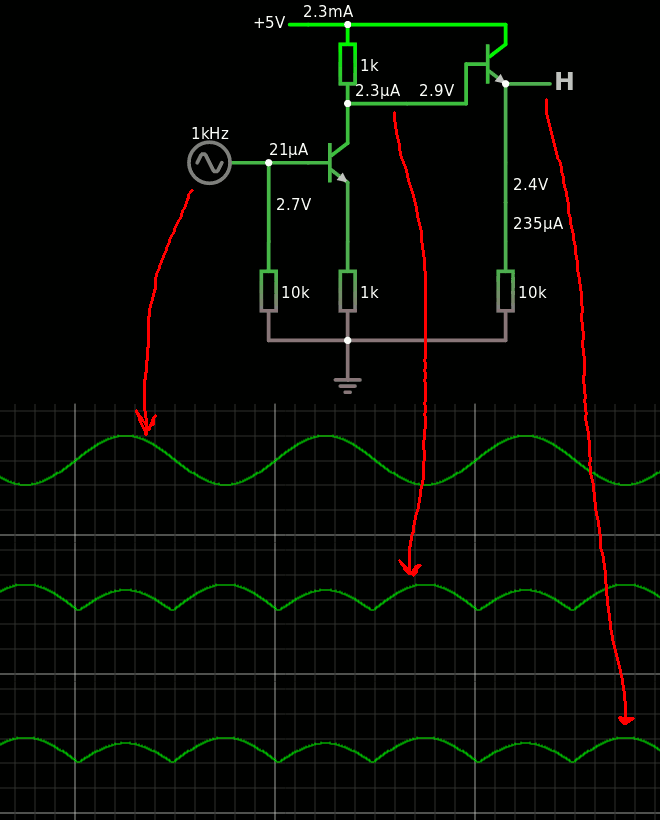

So I was Falstad'ing some ECL/differential amplifier topologies and playing with the resistor values ratios...

I found some strange behaviours with this single-ended circuit when the collector and emitter resistors are equal.

At 5V the turning point is at 3.1V, so I created a sine wave centered around 3V with +/- 1V peaks. The output looks like a rectified version...

The effect disappears when the ratio of the resistors is modified. This might be a desired effect or an unwanted behaviour, and since I'm playing with ECL topologies, I want to avoid this so I need to understand what is going on.

This is important because I would like to save a transistor at the common emitter node so the resistor value must be well chosen. It's good to know that a 1/1 ratio is BAD, and changing it affects the kink point...

But OTOH it opens up potential for fun, such as sound effects :-P

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

This resembles a Concertina phase splitter. So will have to bias the emitter slightly under 1/4 VCC to allow collector slightly above 3/4 VCC to wave a mirror image. Bias it wrong, and voltages collide in the middle. This doesn't stop the base from dumping even more current onto that collision. Thus the unexpected double hump happens. You probably want more than unity gain, so equal resistors was an unfortunate choice to begin.

Are you sure? yes | no

You're obviously way more qualified than me, I'm not sure to understand everything you wrote :-D

Are you sure? yes | no

https://en.wikipedia.org/wiki/Phase_splitter

Forget digital a moment and go analog. Draw two opposing sines that clip neither voltage rails or each other. A mirror pair (since you used equal 1K resistors at same current) of sines as large as could possibly fit. What DC voltage should we measure at the flattened average of each sine? Leave an extra untouched half Volt (or whatever your transistor's VCEsat might be) in the middle for the transistor to operate normally.

Are you sure? yes | no