Well the Baby proper was really a test bed for Williams and Kilburn's Storage Tube which was the first reliable RAM. This stored 1024 bits of data as 32 lines of 32 bits on the back face of a CRT tube. They built the store first to try and improve early radar displays. When they had the store working they added the rest of the Baby to test it.

There is a description of the store here:-

https://en.wikipedia.org/wiki/Williams_tube

and an article about its development here:-

http://www.cs.man.ac.uk/CCS/res/res02.htm#e

I decided that if developing the memory first was good enough for Williams and Kilburn it would work for me. So I started to create the VHDL code for the memory and VGA display.

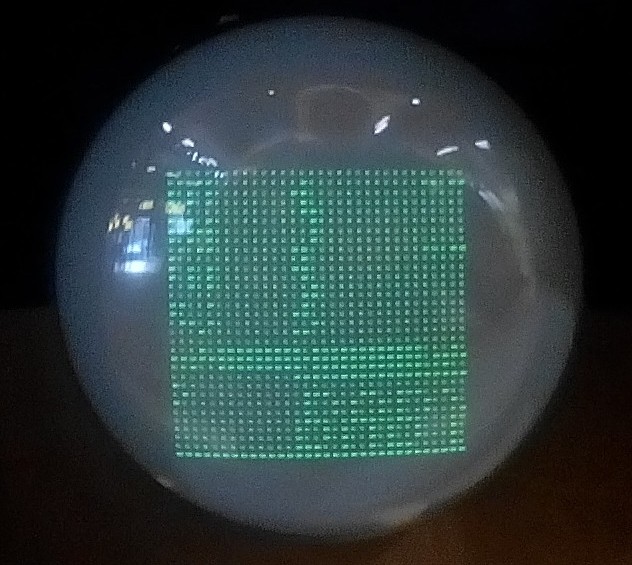

On the Baby the CRT that actually stores the data has a wire mesh over its screen that is used to detect how many electrons travel through the screen as the lines of stored data are scanned. Each bit is stored as either a small dot for a zero or a dash for a 1. There is a second CRT called the monitor tube which normally displays the same pattern as the store proper. Here is the Monitor on the real Baby showing one of the demonstration that is run on the replica at the Museum of Science and Industry in Manchester.

The Spartan 3E chip on the Nexys 2 board used in the project includes block RAM which is used as the Baby store. I configured a portion of this as a 32 x 32 bit RAM. This is equivalent to the hidden Kilburn-Williams store CTR on the Baby. The Monitor tube is replaced by a VGA monitor driven from the VGA port included on the Nexys 2 board.

As the CRT needs to be continually refreshed on the Baby the two CRTs run at the same speed. CPU access is interleaved with the refresh so there is never any conflict.

On the BabyBaby the CPU runs at the same speed as the real Baby, but the VGA display of course runs at a different rate. To cater for this the RAM is set in "dual port" mode. This allows the VGA display to access the RAM independently of the CPU.

I would like to say that I carefully laid out the VGA display layout and it all worked fine. However I didn't. The initial calculated layout did not look good, so I tweaked the counters in the FPGA VGA code until it looked OK when displayed on a standard desktop VGA Display.

dave

dave

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Cool history lesson :-)

Are you sure? yes | no