Do you see what I did here ?

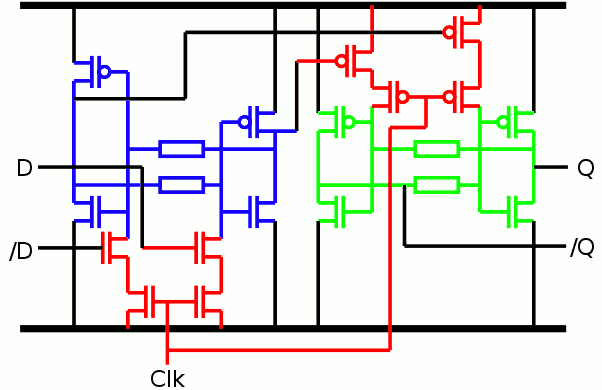

It's a little variation on the previous design, with a nice little trick. It fully uses the complementarity of the transistors to solve some clocking questions.

For a better understanding, I've colored the main 3 blocks :

- the Master block in blue

- the Slave in green

- the clock enable in red

This mirored design now uses a single clock signal, with a fanout of 4. With a sufficiently strong driver, this should solve the possible delay caused by an inverter on the clock, which increases the setup&hold times.

Furthermore, by carefully choosing the power supply voltage and the gate threshold values, we can ensure that there is no overlapping of both phases and no risk of metastability. Just make sure that both FET types are not even slightly "ON" at the same time and you're fine.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.