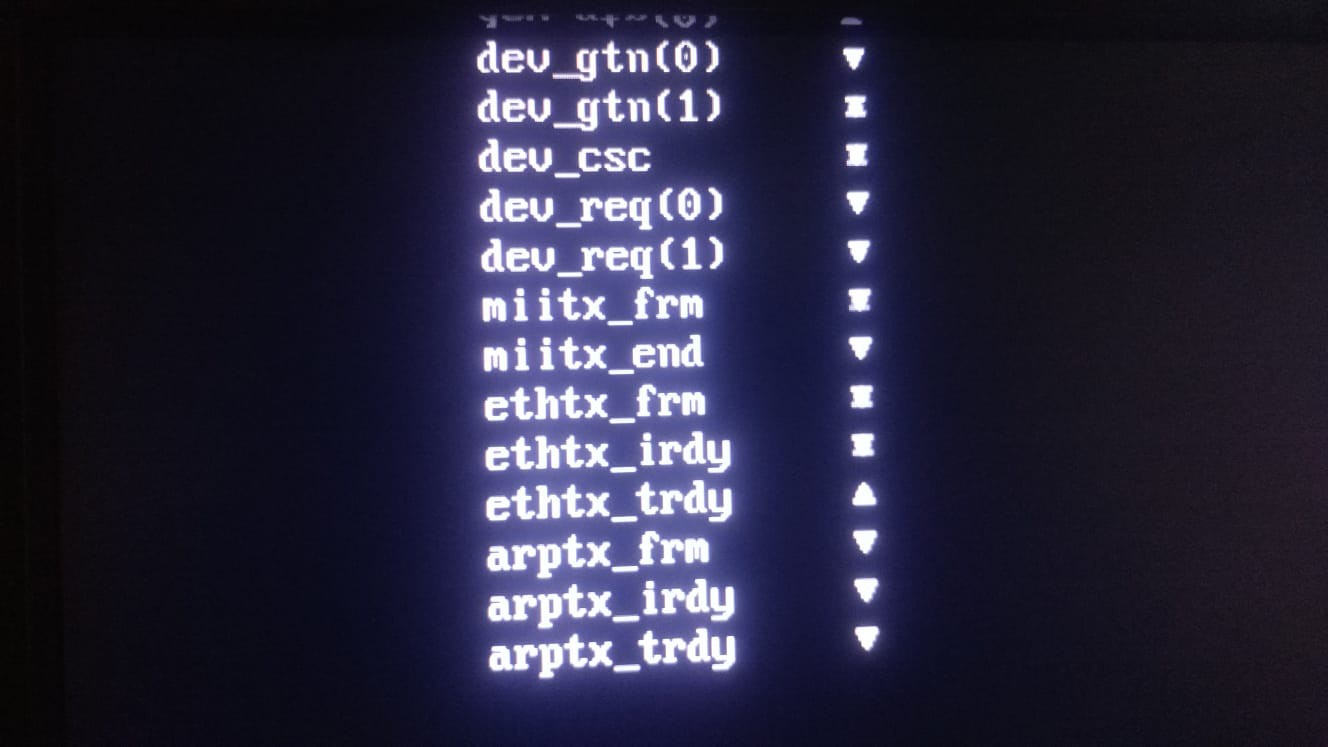

Display testpoint values on screen. It helped me to find deadlock bug on the UDP comm system.

Project files can be found on

https://github.com/hdl4fpga/hdl4fpga/tree/2a0e459e2c5e06b068ccb8dec8f681b24327e238

library/basic/base.vhd library/basic/dpram.vhd library/video/videopkg.vhd library/video/tmds_encoder.vhd library/video/cgafonts.vhd library/video/cga_rom.vhd library/video/cga_adapter.vhd library/video/fonts/bcdfonts.vhd library/video/fonts/cp850x8x8x0to127.vhd library/video/fonts/cp850x8x8x128to255.vhd library/video/fonts/cp850x8x16x0to127.vhd library/video/fonts/cp850x8x16x128to255.vhd library/basic/latency.vhd library/basic/rom.vhd library/video/video.vhd library/video/dvi.vhd library/basic/serlzr.vhd library/basic/barrel.vhd library/sdram/phy_iofifo.vhd library/apps/app_profiles.vhd library/apps/ecp5_profiles.vhd library/apps/ecp5_videopll.vhd library/basic/fifo.vhd library/basic/sync_transfer.vhd library/basic/adder.vhd library/basic/txn_buffer.vhd library/apps/display_tp.vhd

Example of usage

library ieee;

use ieee.std_logic_1164.all;

entity ulx3s is

generic (

debug : boolean := false);

port (

clk_25mhz : in std_logic;

ftdi_rxd : out std_logic;

ftdi_txd : in std_logic := 'U';

ftdi_nrts : inout std_logic := 'U';

ftdi_ndtr : inout std_logic := 'U';

ftdi_txden : inout std_logic := 'U';

btn_pwr_n : in std_logic := 'U';

fire1 : in std_logic := 'U';

fire2 : in std_logic := 'U';

up : in std_logic := 'U';

down : in std_logic := 'U';

left : in std_logic := 'U';

right : in std_logic := 'U';

led : out std_logic_vector(8-1 downto 0);

sw : in std_logic_vector(4-1 downto 0) := (others => 'U');

oled_clk : out std_logic;

oled_mosi : out std_logic;

oled_dc : out std_logic;

oled_resn : out std_logic;

oled_csn : out std_logic;

--flash_csn : out std_logic;

--flash_clk : out std_logic;

--flash_mosi : out std_logic;

--flash_miso : in std_logic;

--flash_holdn : out std_logic;

--flash_wpn : out std_logic;

sd_clk : in std_logic := '-';

sd_cmd : out std_logic; -- sd_cmd=MOSI (out)

sd_d : inout std_logic_vector(4-1 downto 0) := (others => 'U'); -- sd_d(0)=MISO (in), sd_d(3)=CSn (out)

sd_wp : in std_logic := '-';

sd_cdn : in std_logic := '-'; -- card detect not connected

adc_csn : out std_logic;

adc_mosi : out std_logic;

adc_miso : in std_logic := '-';

adc_sclk : out std_logic;

audio_l : out std_logic_vector(4-1 downto 0);

audio_r : out std_logic_vector(4-1 downto 0);

audio_v : out std_logic_vector(4-1 downto 0);

wifi_en : out std_logic := '1'; -- '0' disables ESP32

wifi_rxd : out std_logic;

wifi_txd : in std_logic := '-';

wifi_gpio0 : out std_logic := '1'; -- '0' requests ESP32 to upload "passthru" bitstream

wifi_gpio5 : inout std_logic := '-';

wifi_gpio16 : inout std_logic := '-';

wifi_gpio17 : inout std_logic := '-';

ant_433mhz : out std_logic;

usb_fpga_dp : inout std_logic := 'U';

usb_fpga_dn : inout std_logic := 'U';

usb_fpga_bd_dp : inout std_logic := 'U';

usb_fpga_bd_dn : inout std_logic := 'U';

usb_fpga_pu_dp : inout std_logic := 'U';

usb_fpga_pu_dn : inout std_logic := 'U';

sdram_clk : inout std_logic;

sdram_cke : out std_logic;

sdram_csn : out std_logic;

sdram_wen : out std_logic;

sdram_rasn : out std_logic;

sdram_casn : out std_logic;

sdram_a : out std_logic_vector(13-1 downto 0);

sdram_ba : out std_logic_vector(2-1 downto 0);

sdram_dqm : inout std_logic_vector(2-1 downto 0) := (others => 'U');

sdram_d : inout std_logic_vector(16-1 downto 0) := (others => 'U');

gpdi_d : out std_logic_vector(4-1 downto 0);

gpdi_dn : out std_logic_vector(4-1 downto 0);

gpdi_cec : inout std_logic := '-';

gpdi_sda : inout std_logic := '-';

gpdi_scl : inout std_logic := '-';

gp : inout std_logic_vector(28-1 downto 0) := (others => 'Z');

gn : inout std_logic_vector(28-1 downto 0) := (others => 'Z');

gp_i : in std_logic_vector(12 downto 9);

user_programn : out std_logic := '1'; -- '0' loads next bitstream from SPI FLASH (e.g. bootloader)

shutdown : out std_logic := '0'); -- '1' power off the board, 10uA sleep

alias rmii_tx_en : std_logic is gn(10);

alias rmii_tx0 : std_logic is gp(10);

alias rmii_tx1 : std_logic is gn(9);

alias rmii_rx0 : std_logic is gn(11);

alias rmii_rx1 : std_logic is gp(11);

alias rmii_crsdv : std_logic is gp(12);

alias rmii_nintclk : std_logic is gn(12);

alias rmii_mdio : std_logic is gn(13);

alias rmii_mdc : std_logic is gp(13);

alias hdmi0_blue : std_logic is gpdi_d(0);

alias hdmi0_green : std_logic is gpdi_d(1);

alias hdmi0_red : std_logic is gpdi_d(2);

alias hdmi0_clock : std_logic is gpdi_d(3);

constant clk25mhz_freq : real := 25.0e6;

end;

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

library hdl4fpga;

use hdl4fpga.base.all;

use hdl4fpga.videopkg.all;

use hdl4fpga.ipoepkg.all;

use hdl4fpga.app_profiles.all;

use hdl4fpga.ecp5_profiles.all;

library ecp5u;

use ecp5u.components.all;

architecture display_tp of ulx3s is

constant video_mode : video_modes := mode600p24bpp;

constant video_param : video_record := videoparam(video_mode);

signal video_pixel : std_logic_vector(0 to setif(

video_param.pixel=rgb565, 16, setif(

video_param.pixel=rgb888, 32, 0))-1);

signal sys_rst : std_logic;

signal sys_clk : std_logic;

signal videoio_clk : std_logic;

signal video_clk : std_logic;

signal video_shift_clk : std_logic;

signal video_lck : std_logic;

signal video_hzsync : std_logic;

signal video_vtsync : std_logic;

signal dvid_crgb : std_logic_vector(7 downto 0);

signal tp : std_logic_vector(0 to 6-1);

begin

sys_rst <= '0';

videopll_e : entity hdl4fpga.ecp5_videopll

generic map (

clkref_freq => clk25mhz_freq,

default_gear => 2,

video_param => video_param)

port map (

clk_ref => clk_25mhz,

videoio_clk => videoio_clk,

video_clk => video_clk,

video_shift_clk => video_shift_clk,

video_lck => video_lck);

tp <= (fire1, fire2, up, down, left, right);

displaytp_e : entity hdl4fpga.display_tp

generic map (

timing_id => video_param.timing,

video_gear => 2,

num_of_cols => 1,

field_widths => (15,10,3),

labels =>

"fire1" & NUL &

"fire2" & NUL &

"up" & NUL &

"down" & NUL &

"left" & NUL &

"right" & NUL)

port map (

sweep_clk => video_clk,

tp => tp,

video_clk => video_clk,

video_shift_clk => video_shift_clk,

video_hs => video_hzsync,

video_vs => video_vtsync,

video_pixel => video_pixel,

dvid_crgb => dvid_crgb);

ddr_g : for i in gpdi_d'range generate

signal q : std_logic;

begin

oddr_i : oddrx1f

port map(

sclk => video_shift_clk,

rst => '0',

d0 => dvid_crgb(2*i),

d1 => dvid_crgb(2*i+1),

q => q);

olvds_i : olvds

port map(

a => q,

z => gpdi_d(i),

zn => gpdi_dn(i));

end generate;

end;

Miguel Angel

Miguel Angel

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.