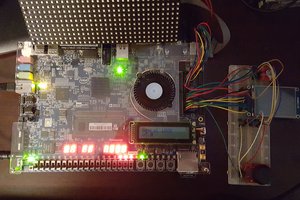

The GitHub repository for the FPGA core itself can be found HERE. The core is what most of this project is focused on, but there will be a lot of hardware testing along with it.

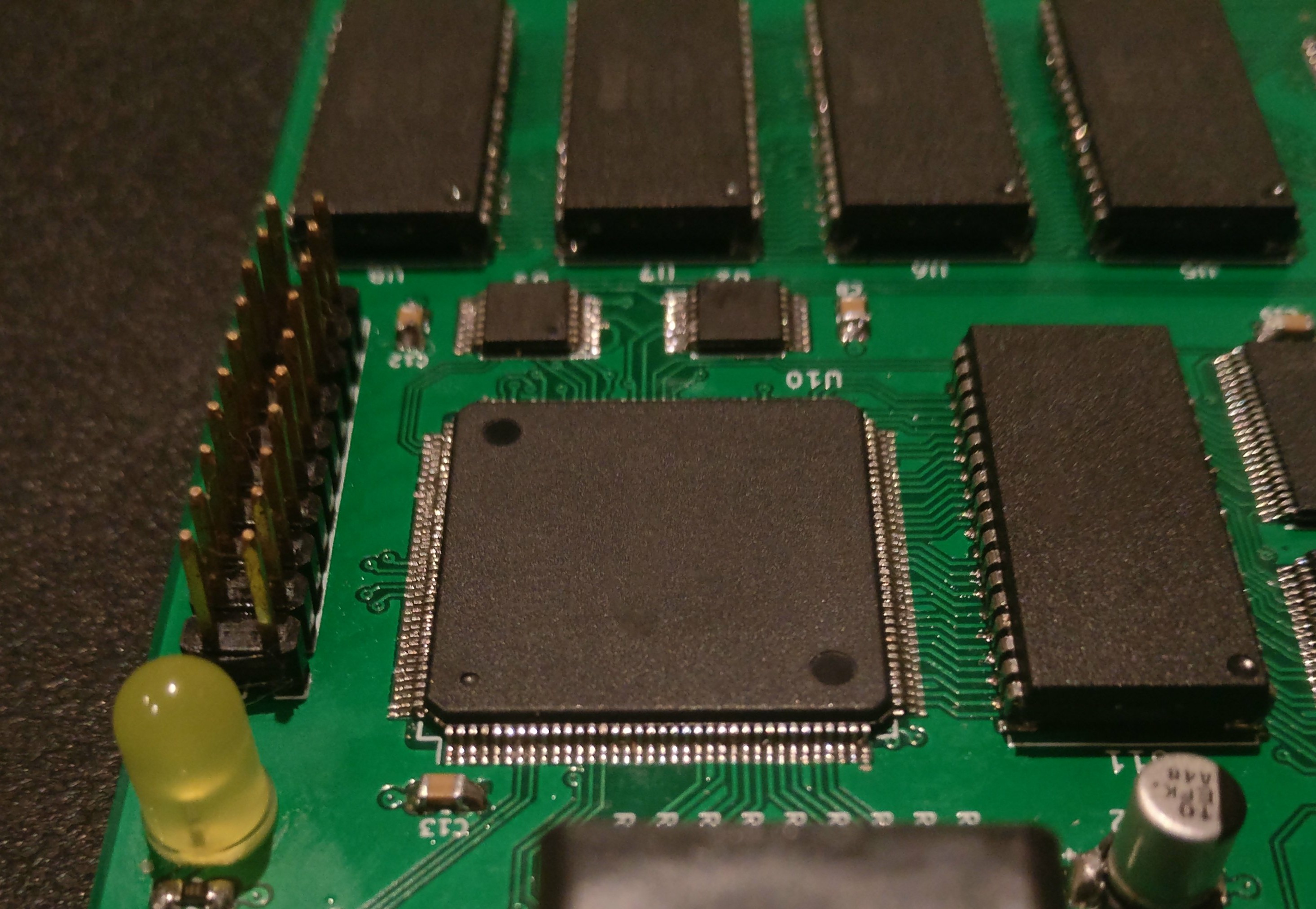

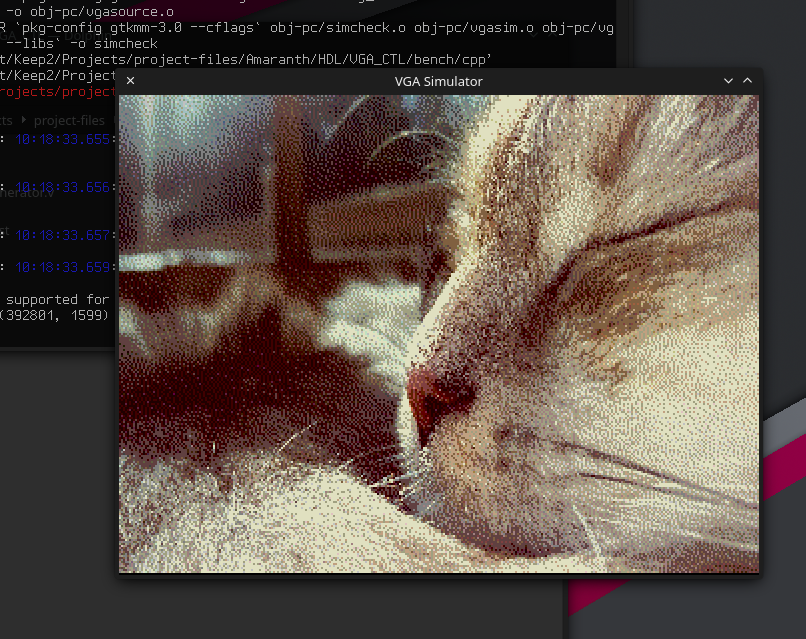

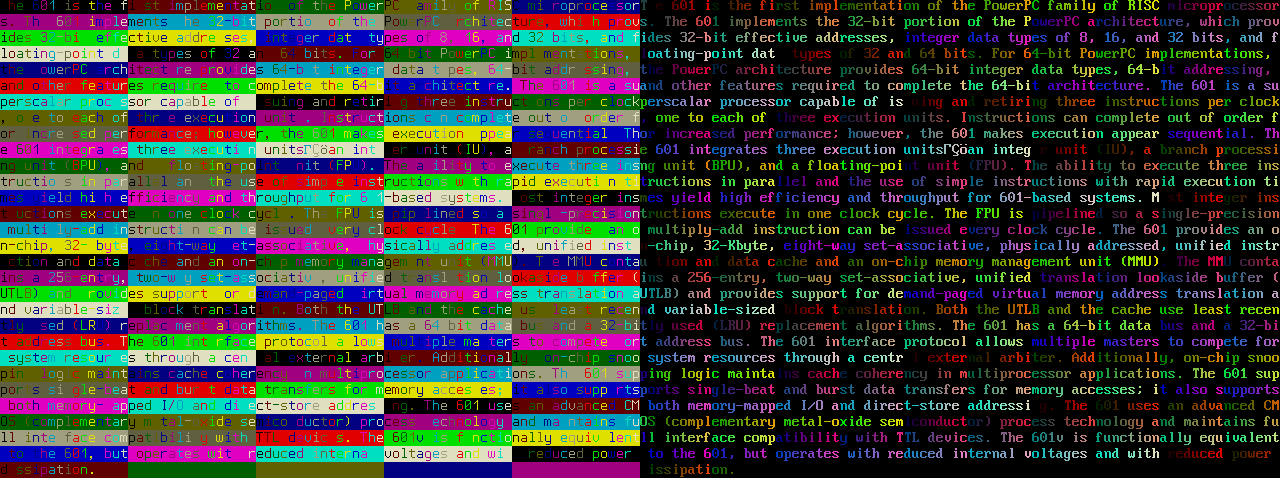

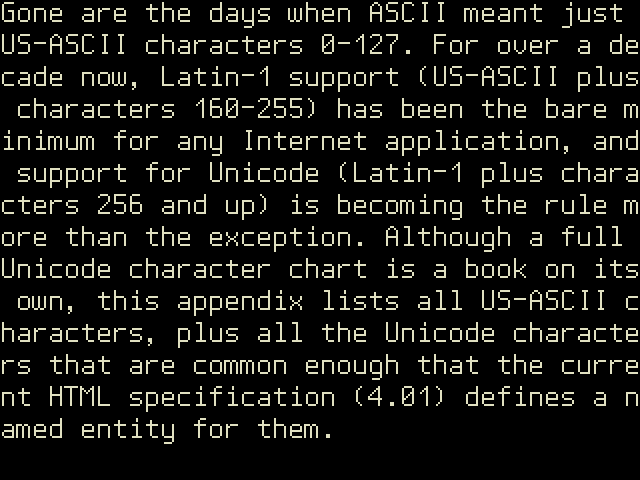

Diapason : m68k homebrew with FPGA graphics

An m68k homebrew with an FPGA acting as a VGA graphics controller

Carson Herrington

Carson Herrington

The other stuff

The other stuff

Jorj Bauer

Jorj Bauer

Wenting Zhang

Wenting Zhang

Matt Stock

Matt Stock

Hmm, I'd love the schematics in an editable form (KiCad, EagleCad) for not only this project but your other 68k project with the 68030. Looking to base myself on both these designs and work from there on my own custom DIY approach. Can you drop a link?